### Future Memories and Today's Opportunities

Tom Coughlin, Coughlin Associates Jim Handy, Objective Analysis

Coughlin Associates

### Cataclysmic Changes Coming Soon

• Scaling Limits

- We can't make transistors any smaller

• New Storage Hierarchies

- You think SSDs were disruptive? Just wait!

• More Layers Will Be Added

- It's all about touch rates and response time

• Processors Must Adapt

# SCALING LIMITS

© 2016 Coughlin Associates & Objective Analysis

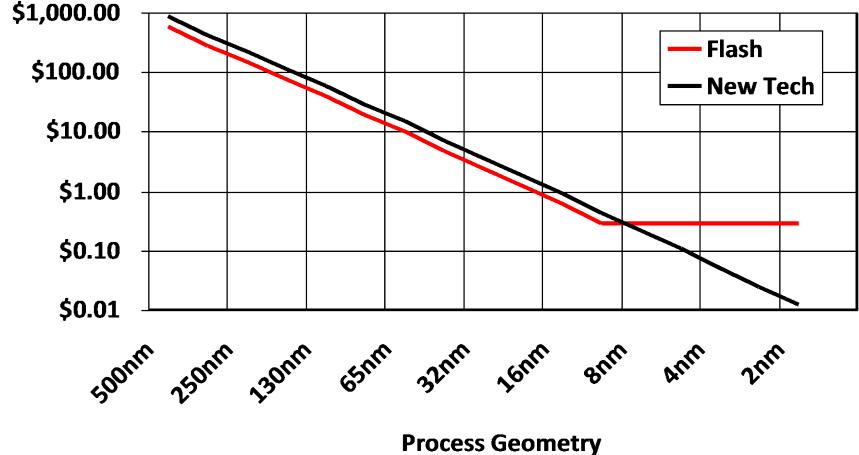

### Scaling Limits Create Opportunities for New Memories

### No Shortage of Options

### Today's Memories Are Limited

|                | SRAM       | DRAM           | ROM                      | EEPROM            | NOR  | NAND  |

|----------------|------------|----------------|--------------------------|-------------------|------|-------|

| Nonvolatile    | No         | No             | Yes                      | Yes               | Yes  | Yes   |

| Erasable       | Yes        | Yes            | No                       | Yes               | Yes  | Yes   |

| Programmable   | Yes        | Yes            | Factory                  | Yes               | Yes  | Yes   |

| Smallest Write | Byte       | Byte           | N/A                      | Byte              | Byte | Page  |

| Smallest Read  | Byte       | Page           | Byte                     | Byte              | Byte | Page  |

| Read Speed     | V Fast     | Fast           | Fast                     | Fast              | Fast | Slow  |

| Write Speed    | V Fast     | Fast           | N/A                      | Slow              | Slow | Slow  |

| Active Power   | High       | Med            | Med                      | Med               | Med  | Med   |

| Sleep Power    | V Low      | High           | Zero                     | Zero              | Zero | Zero  |

| Price/GB       | High       | Low            | Low                      | High              | Med  | V Low |

| Applications   | Small Fast | Main<br>Memory | Stable<br>Code<br>Volume | Serial #,<br>Trim | Code | Data  |

### **Emerging Memories Perform Better**

|                | MRAM  | ReRAM | FRAM      | PCM      | XPoint         |

|----------------|-------|-------|-----------|----------|----------------|

| Nonvolatile    | Yes   | Yes   | Yes       | Yes      | Yes            |

| Erasable       | Yes   | Yes   | Yes       | Yes      | Yes            |

| Programmable   | Yes   | Yes   | Yes       | Yes      | Yes            |

| Smallest Write | Byte  | Byte  | Byte      | Byte     | Byte           |

| Smallest Read  | Byte  | Byte  | Byte      | Byte     | Byte           |

| Read Speed     | Fast  | Fast  | Fast      | Fast     | Fast           |

| Write Speed    | Fast  | Fast  | Fast      | Fast     | Fast           |

| Active Power   | Low   | Med   | Low       | High     | High?          |

| Sleep Power    | Low   | Low   | Low       | Low      | Low            |

| Price/GB       | High  | High  | High      | High     | High?          |

| Applications   | Niche | TBD   | Low Power | Obsolete | Main<br>Memory |

## NEW STORAGE HIERARCHIES

© 2016 Coughlin Associates & Objective Analysis

8

ZAA A AL

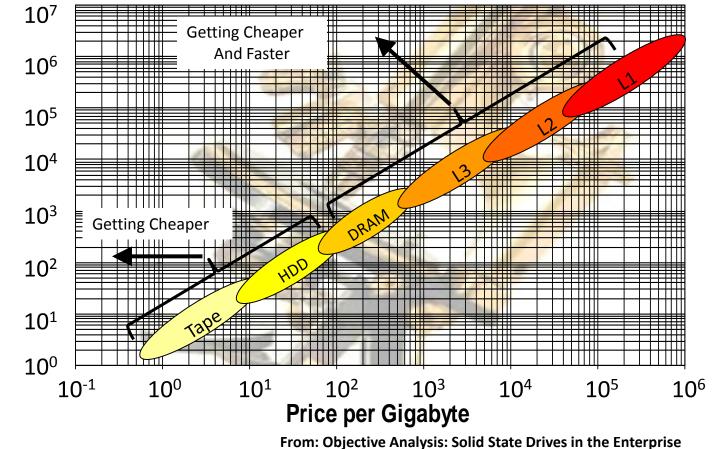

# Memory/Storage Hierarchy 2000

Bandwidth (MB/s)

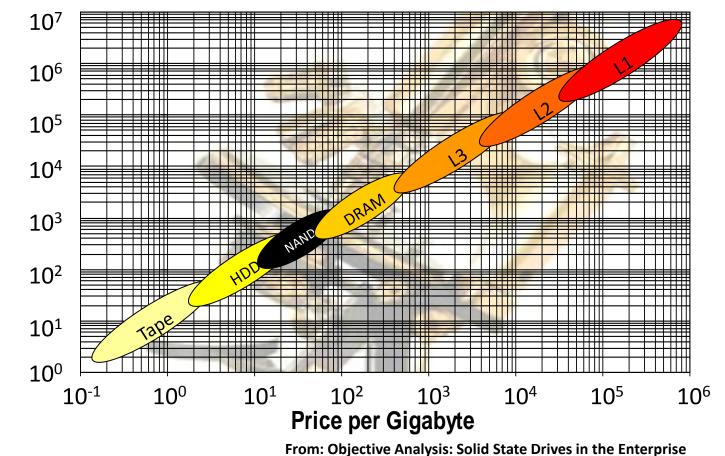

### NAND Flash SSDs Today Make Sense

Bandwidth (MB/s)

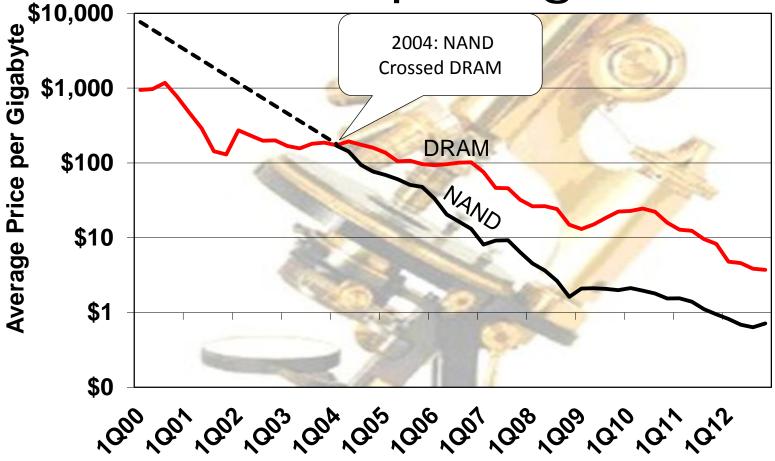

### Cost Brought Flash Into Computing

From: Objective analysis: Hybrid Drives: How, Why, & When?

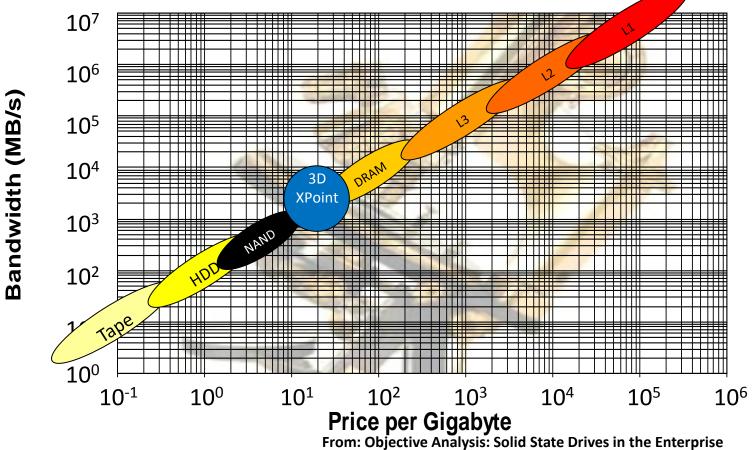

### 3D XPoint Will Do The Same In 2017

### Intel's & Micron's 3D XPoint Intro

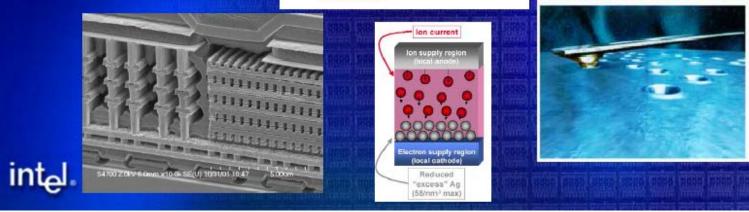

#### 3D XPoint™ Technology**:** An Innovative, High-Density Design

#### **Cross Point Structure**

Perpendicular wires connect submicroscopic columns. An individual memory cell can be addressed by selecting its top and bottom wire.

#### **Non-Volatile**

3D XPoint<sup>®</sup> Technology is non-volatile—which means your data doesn't go away when your power goes away—making it a great choice for storage.

#### **High Endurance**

Unlike other storage memory technologies, 3D XPoint<sup>\*\*</sup> Technology is not significantly impacted by the number of write cycles it can endure, making it more durable.

#### Stackable

These thin layers of memory can be stacked to further boost density.

#### Selector

Whereas DRAM requires a transistor at each memory cell—making it big and expensive—the amount of voltage sent to each 3D XPoint<sup>™</sup> Technology selector enables its memory cell to be written to or read without requiring a transistor.

Memory Cell Each memory cell can store a single bit of data.

#### **Transforming the Memory Hierarchy**

For the first time, there is a fast, inexpensive and non-volatile memory technology that can serve as system memory and storage.

#### ~8x to 10x Greater Density than DRAM<sup>1</sup>

3D XPoint<sup>®</sup> Technology's simple, stackable, transistor-less design packs more memory into less space, which is critical to reducing cost.

3D XPoint<sup>™</sup> Technology

Processor uphlin Associates & Objective A

DRAM

3D XPoint<sup>™</sup> Technology

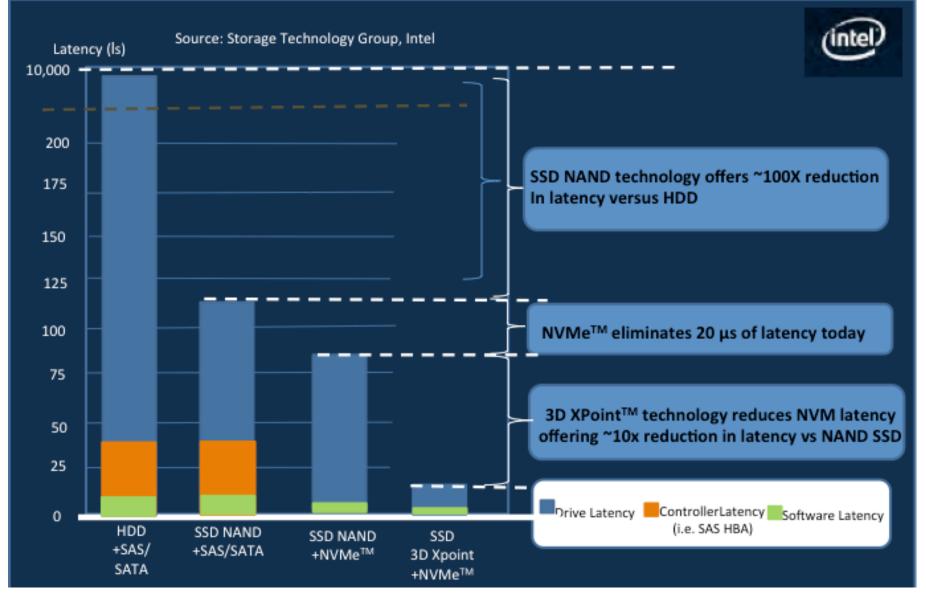

### **3D XPoint Slashes Latency**

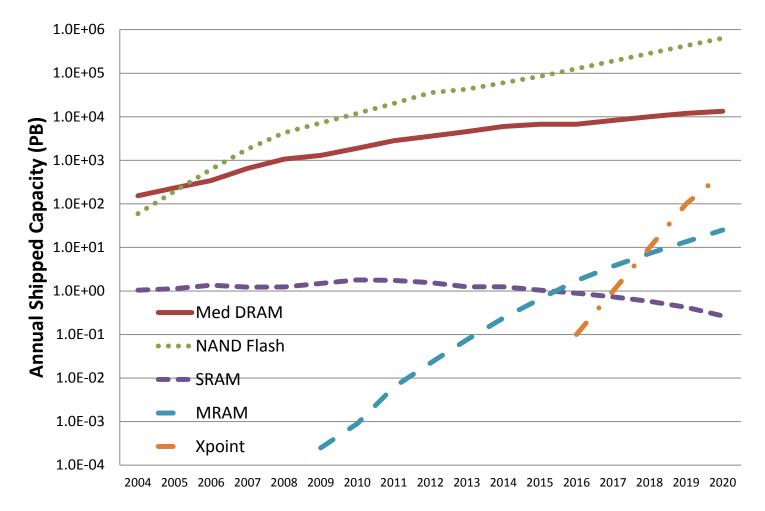

#### ANNUAL SHIPPED CAPACITY (PB) FOR DRAM, NAND FLASH, SRAM, MRAM AND 3D XPOINT

2015 EMERGING NON-VOLATILE MEMORY & SPIN LOGIC TECHNOLOGY AND MANUFACTURING REPORT, Coughlin Associates, 2015, http://www.tomcoughlin.com/techpapers.htm

# WHY MORE STORAGE LAYERS

© 2016 Coughlin Associates & Objective Analysis

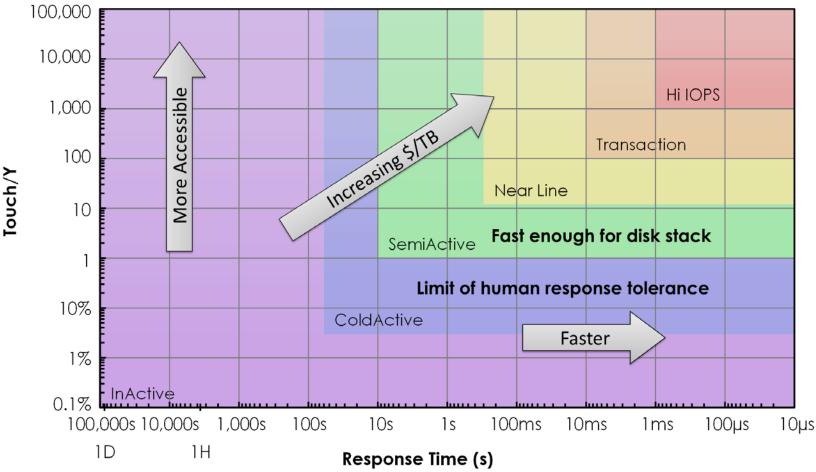

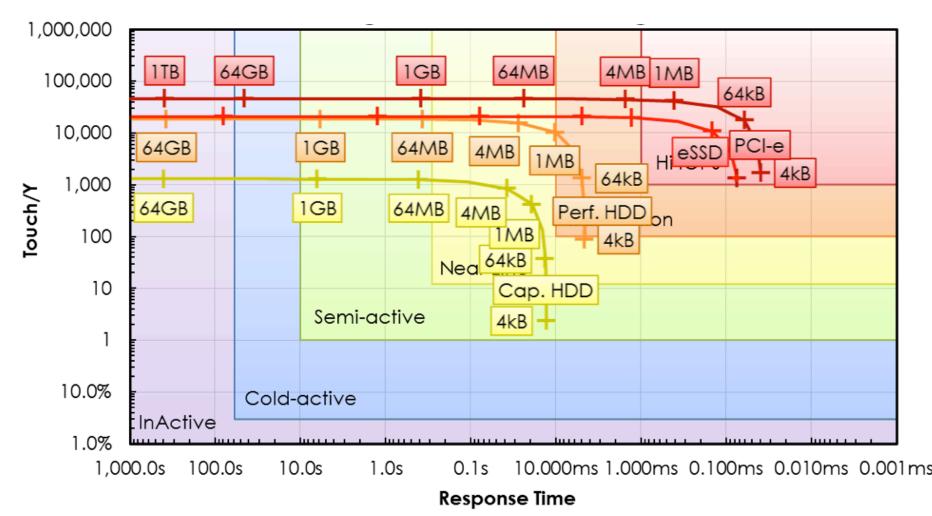

### "Touch Rates" vs. Response Time By Application

2015 EMERGING NON-VOLATILE MEMORY & SPIN LOGIC TECHNOLOGY AND MANUFACTURING REPORT, Coughlin Associates, 2015, http://www.tomcoughlin.com/techpapers.htm

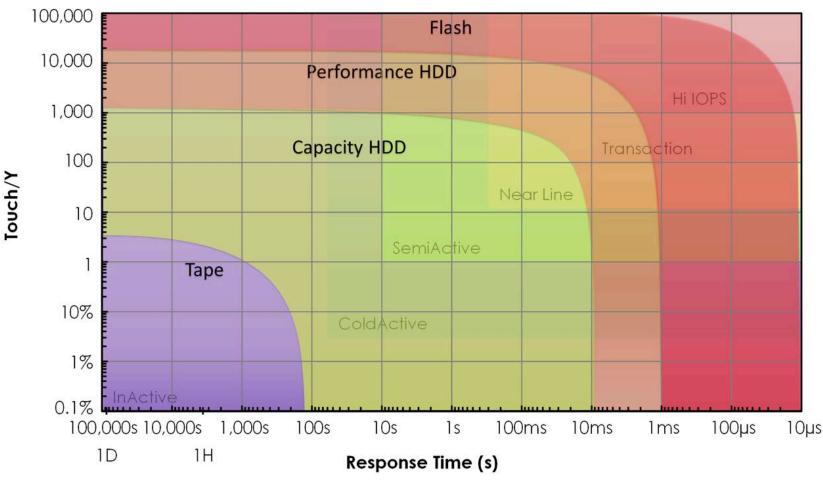

### Mapping This To Storage Technologies

2015 EMERGING NON-VOLATILE MEMORY & SPIN LOGIC TECHNOLOGY AND MANUFACTURING REPORT, Coughlin Associates, 2015, http://www.tomcoughlin.com/techpapers.htm

© 2016 Coughlin Associates & Objective Analysis

### **Real Products Mapped**

2015 EMERGING NON-VOLATILE MEMORY & SPIN LOGIC TECHNOLOGY AND MANUFACTURING REPORT, Coughlin Associates, 2015, http://www.tomcoughlin.com/techpapers.htm

# PROCESSORS MUST ADAPT

© 2016 Coughlin Associates & Objective Analysis

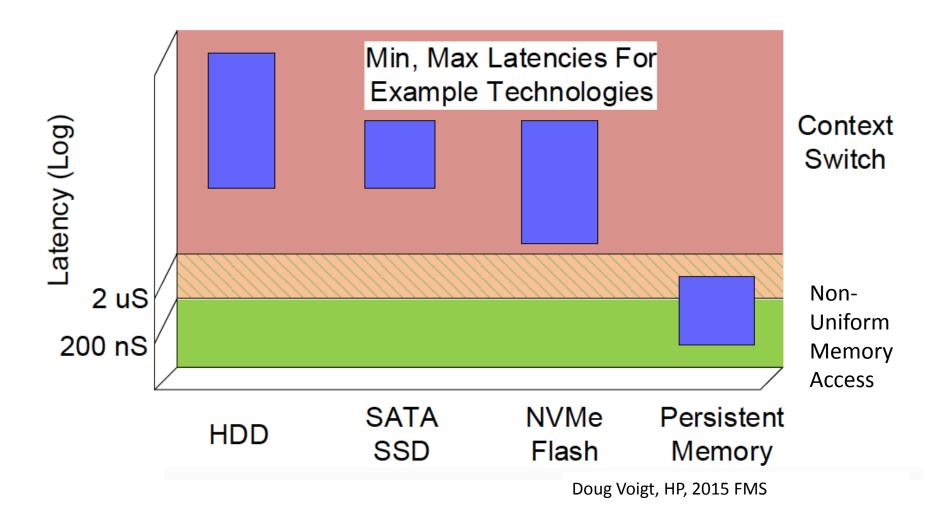

### **Context Switches Become The Issue**

### **Persistent Memory Implications**

- Retains data during a power loss

- Instant recovery of state before power down

- Lower latencies than disk

- Lower power than DRAM

- Allows persistent states for Remote Direct Memory Access (RDMA)

- Supports "logic-in-memory architecture"

- Could lead to new distributed computer architectures

### Summary

- Scaling limits open doors to new memories

New architectures will create other opportunities

- New architectures will create other opportunities

- NAND is <u>NOW</u>

- 3D XPoint is coming soon

- Performance drives need for new layers

- New layers will drive new processor architectures

Application programs will also adapt

## Thank You!

Tom Coughlin, Coughlin Associates Jim Handy, Objective Analysis