# **Unleashing MRAM as Persistent Memory**

Andrew J. Walker PhD Spin Transfer Technologies

# Contents

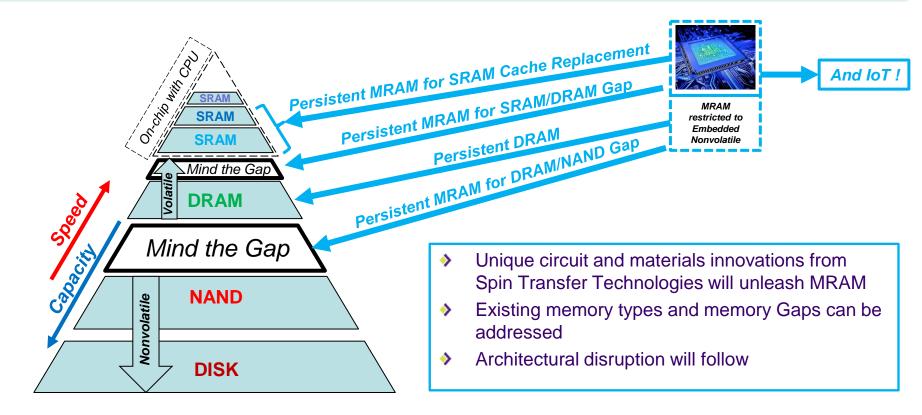

# The Creaking Pyramid

- Challenges with the Memory Hierarchy

- What and Where is MRAM ?

- State of the Art pMTJ

- Unleashing MRAM

- MRAM Unbound

# The Creaking Pyramid

© 2018 SNIA Persistent Memory Summit. All Rights Reserved.

References: S.H. Kang et al., IEDM17., Various IEDMs; D. James, ASMC 2013; Techinsights 2014

3

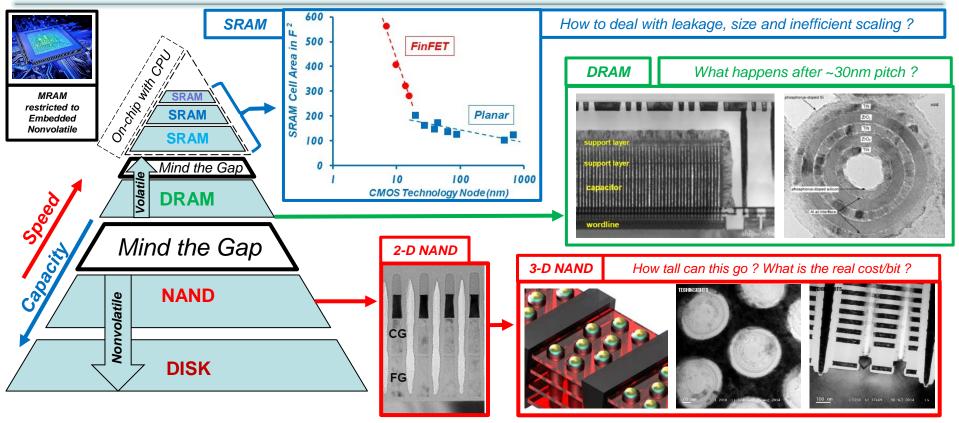

# Challenges within the Memory Hierarchy

#### ♦ SRAM

- Ever larger cache capacities needed

- Inefficient scaling in FinFET CMOS

- Large leakage currents dominating power dissipation

#### DRAM

- Scalability reaching fundamental limits close to 30 nm pitch

- Refresh power dissipation only getting worse

- Not monolithically 3-D stackable

#### NAND

- 3-D transition made but how tall can it go?

- Can it be laterally shrunk ?

- What is the real cost per bit?

#### The Gaps

- Does 3D XPoint<sup>™</sup> fit the bill ?

- Can ReRAM really be made to work ?

- What else can fill The Gaps ?

© 2018 SNIA Persistent Memory Summit. All Rights Reserved.

References: S.H. Kang et al., IEDM17., D. James, ASMC 2013

# What is MRAM ?

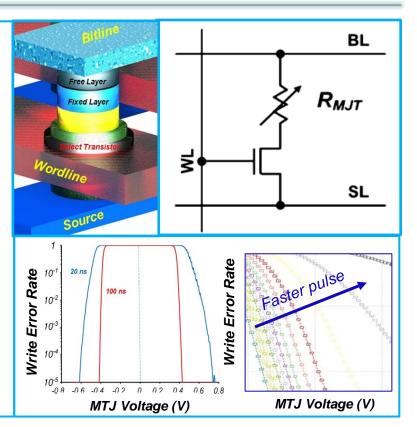

## Spin-Transfer Torque Magnetic RAM

- A magnetic ReRAM using a perpendicular Magnetic Tunnel Junction (*pMTJ*)

- Writing: flip <u>M</u><sub>free</sub> vector using electron spin to be parallel or anti-parallel with <u>M</u><sub>fixed</sub>

- Writing is stochastic <u>highly unusual</u> for solid-state memory with mathematical description

- Reading: monitor current through MTJ

- <u>M</u><sub>fixed</sub> and <u>M</u><sub>free</sub> parallel gives low resistance

- $\underline{M}_{fixed}$  and  $\underline{M}_{free}$  anti-parallel gives higher resistance

- Physics: the relative directions of <u>M</u><sub>fixed</sub> and <u>M</u><sub>free</sub> alter the Quantum Mechanical tunneling <u>transmission</u> <u>probability</u> through a thin MgO layer resulting in a <u>resistance change</u>

## Emerging as the embedded NV memory of choice in advanced CMOS

- Lower voltage and fewer masks than traditional Flash

- But.... Stochastic behavior limiting MRAM to embedded NV

- Low <u>Write Error Rates</u> need <u>high switching current</u> and <u>long write pulses</u> which cause MgO <u>wearout</u> which limits <u>endurance</u>

- And...Retention and endurance are strongly inversely linked

- NV <u>retention</u> needs stiff <u>M</u><sub>free</sub> which needs <u>high switching current</u> which causes MgO <u>wearout</u> which limits <u>endurance</u>

- Is MRAM confined to the embedded NV "cage" ?

# State of the Art pMTJ

- Retention Endurance Switching Current engineering through:

- Scaling

- Magnetic materials engineering

## Scaled soft magnetic pMTJ allows:

- Lower switching current

- Lower write power dissipation

- High endurance

- Smaller bitcells

- Some level of persistence

## "Conservation of Misery"

- Are R<sub>low</sub> and R<sub>high</sub> sufficiently separated ?

- Manufacturing control and distributions

- Are SRAM/DRAM really replaceable ?

- Are The Gaps Fillable ?

- What can be done to help unleash MRAM?

IBM/Samsung\*\*\*

414 with the 507 ADM 35 DL 39 WUS

10 nm

Conventional

Conventional (Main memory & eNVM)

State Memory:  $\Delta > 60$ C :  $\Delta \sim 60$

∆ Engineered for Cache memory

$\Lambda = 40 \sim 50$

Conventional

Scalin

with  $\Delta$  engineering Larger current

Time

$\Delta: 70 \sim 90$

$2 \therefore \Lambda < 40$

MTJ diameter

Enhance size dependence

Larger Memory Cell

50.7µA

Current

Factor (Δ)

**Thermal Stability**

100.0

80.0

(**Y**n) 60.0

WRITE (

20.0

∆ engineered

Smaller curren Toshiba\*\*

Toshiba\*\*

P write

AP write

•

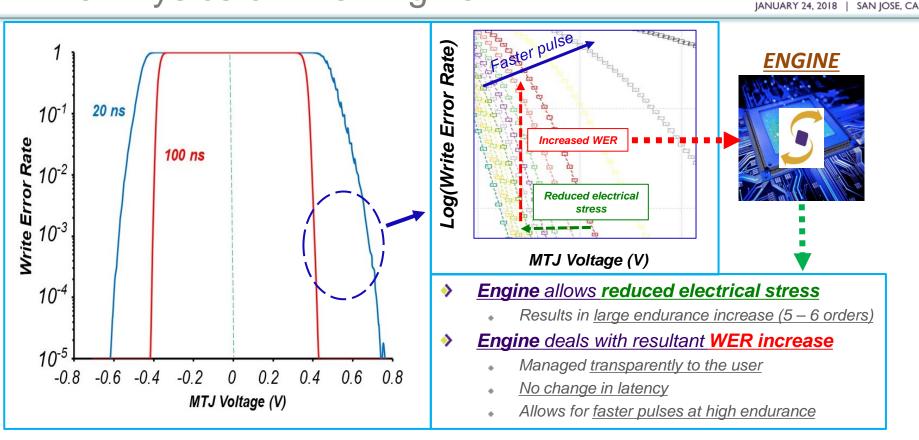

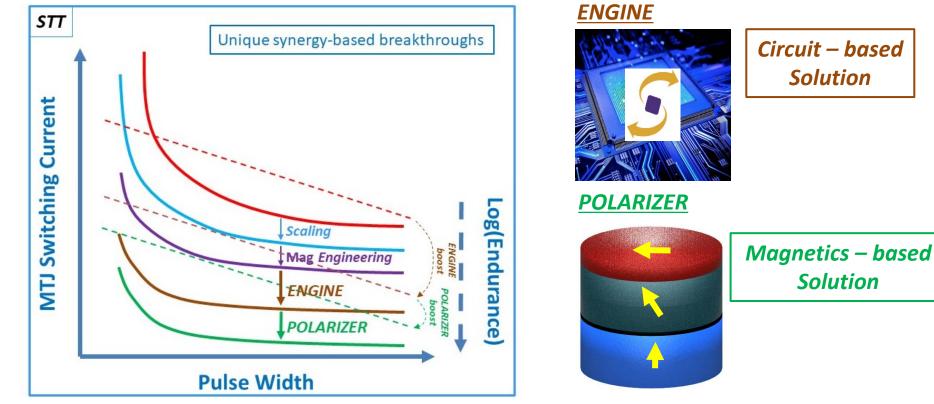

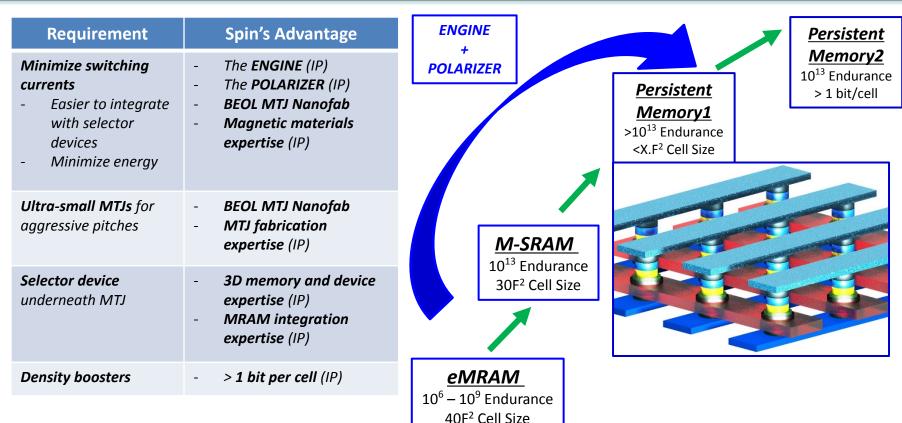

## Unleash MRAM with Spin Transfer Technologies

## **Unique Facility**

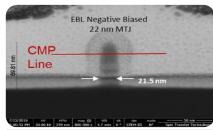

<u>Smaller pMTJ</u> 10ns R/W times Sub-20nm pillars Gb Densities Advanced process nodes Partnered w/TEL

# Unique Magnetics Polarizer

Patented pMTJ Enhancement Faster Switching Lowers R/W current Critical for smaller geometries Heavily Patented

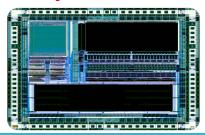

#### **Unique Circuits**

Endurance Engine Increases Endurance by up to six orders Eliminates R/W Errors Shortens time to high yield.

#### © 2018 SNIA Persistent Memory Summit. All Rights Reserved.

#### 9

## Unleash MRAM with Spin Transfer Technologies

#### ♦ STT's **Engine** – The "SanDisk of MRAM" and The Benefit of Synergy

- Significantly reduces the switching current requirements

- Enhances speed to 10ns

- Boosts endurance by 5 to 6 orders of magnitude with no retention change .

- Allows unique embedded NV and SRAM-like capabilities .

- Tuned to anyone's MRAM .

- Purely circuit-based with no materials or process changes .

- No user-visible errors

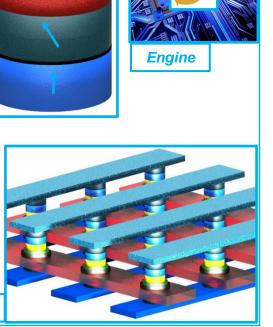

#### STT's **Polarizer** ♦

- Significantly reduces switching current requirements

- Increased switching efficiency .

- Enhances free layer switching speed .

- Enhances read disturb stability

#### STT's Magnetics ♦

Local highly flexible/fast MRAM fab – capable of 1x/2x nm pMTJs

**Magnetics**

**High Density**

**BEOL MTJ integration**

#### STT's High Density Persistent Memory and Magnetic DRAM ♦

- Selector devices/processes

- High density magnetics

**Polarizer**

# The Physics of The Engine

© 2018 SNIA Persistent Memory Summit. All Rights Reserved.

SAN IOSE, CA

© 2018 SNIA Persistent Memory Summit. All Rights Reserved.

## Unleash MRAM with Spin Transfer Technologies

© 2018 SNIA Persistent Memory Summit. All Rights Reserved.

SAN IOSE, CA

IANUARY 24, 2018

# MRAM Unbound