#### Future of Persistent Memory, DRAM and SSD Form Factors Aligned with New System Architectures

Arthur Sainio

Director, Product Marketing, SMART Modular Technologies

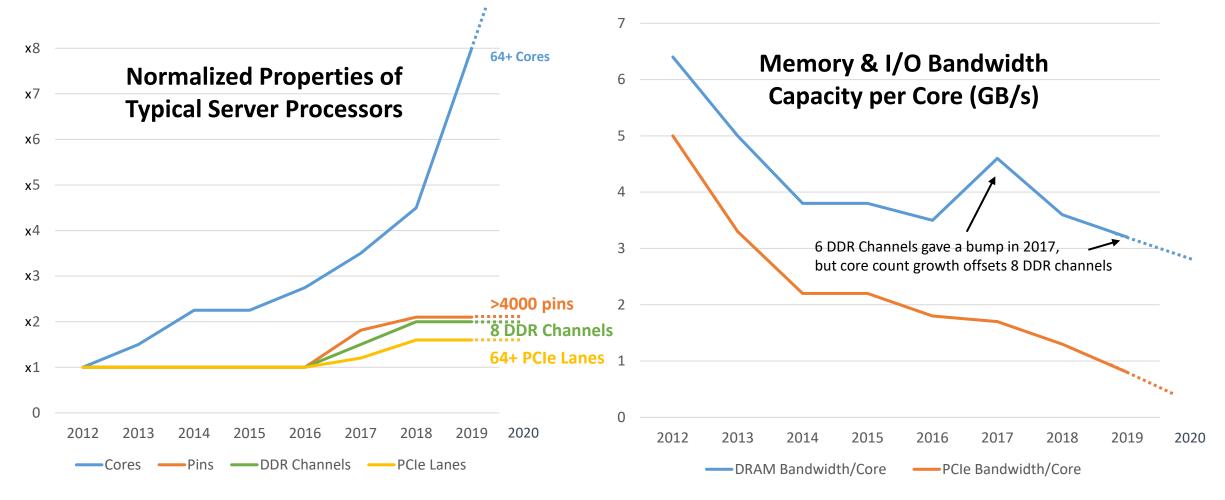

### **Large Datasets Need Memory that Scales**

#### Processor memory and I/O technologies ...

... are being stretched to their limits

More than 2X digital data will be created over the next five years compared to the combined amount since the advent of digital storage (Source; IDC, Mar 2020)

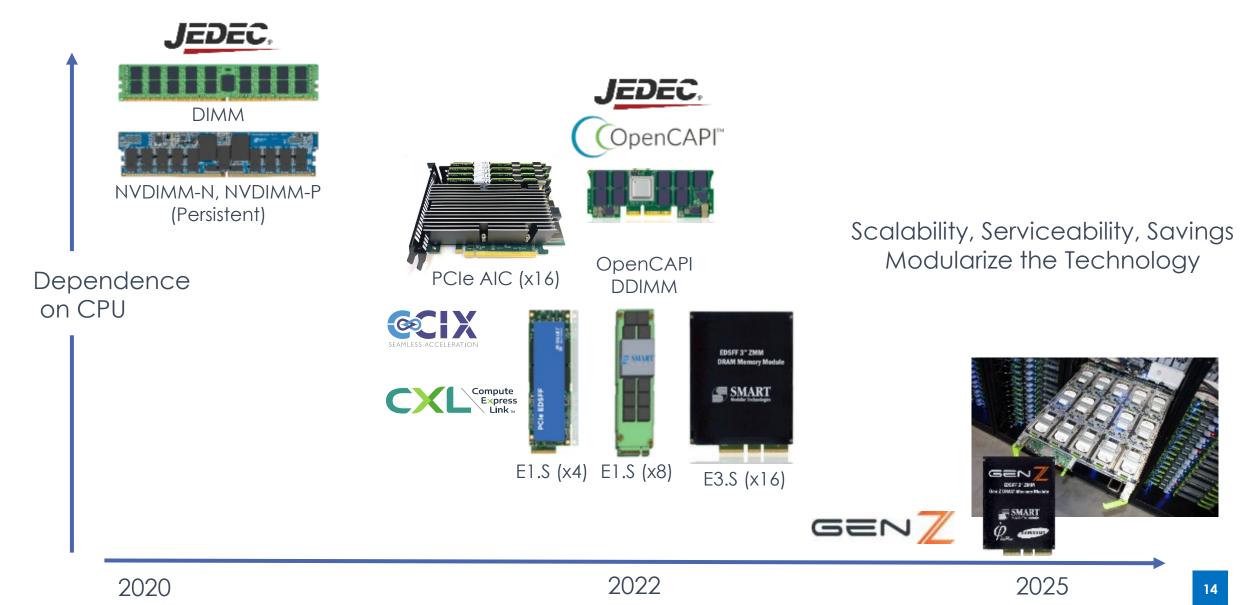

# **Form Factor Migration**

# Performance

| Direct attached<br>(Parallel Bus)<br>100's of GB<br>DIMM<br>DIMM<br>NVDIMM-N, NVDIMM-P<br>(Persistent) |                       |                          | Serial attache<br>and PCIe attac<br>100's of GB to | ched                      |                             | Network Attached<br>TB's to PB's            |

|--------------------------------------------------------------------------------------------------------|-----------------------|--------------------------|----------------------------------------------------|---------------------------|-----------------------------|---------------------------------------------|

|                                                                                                        |                       | E1.S (x4)                |                                                    | Memory Module             | OpenCAPI                    |                                             |

|                                                                                                        | DDR DIMM              | E1.S 1C (x4)             | E1.S 2C (x8)                                       | E3.S   AIC (x16)          | E3 with x8 (2C)             | Across network                              |

| Current<br>Generation<br>*                                                                             | DDR4@3200<br>25.6GB/s | PCIe-Gen4-x4<br>7.8GB/s  | PCIe-Gen4-x8<br>15.7GB/s                           | PCIe-Gen4-x16<br>31.5GB/s | OMI<br>25.6 GB/s<br>8 Ianes | RDMA<br>(Fabric and work load<br>dependent) |

| Future<br>Generation<br>**                                                                             | DDR5@4800<br>63.0GB/s | PCIe-Gen5-x4<br>15.7GB/s | PCIe-Gen5-x8<br>31.5GB/s                           | PCIe-Gen5-x16<br>63.0GB/s | DDR5 DDIMM<br>(TBD) GB/s    | Gen-Z, NVMe-oF (TBD)                        |

\* Source(s): https://en.wikipedia.org/wiki/PCI\_Express#History\_and\_revisions

https://en.wikipedia.org/wiki/DDR4\_SDRAM#JEDEC\_standard\_DDR4\_module

https://www.smartm.com/media/press-releases/smart-modular-to-showcase-its-ddr4-differential-dimm-at-the-flash-memory-summit

\*\* Source(s): https://www.tomshardware.com/news/ddr5-6400-ram-benchmarks-major-performance-gains-ddr4

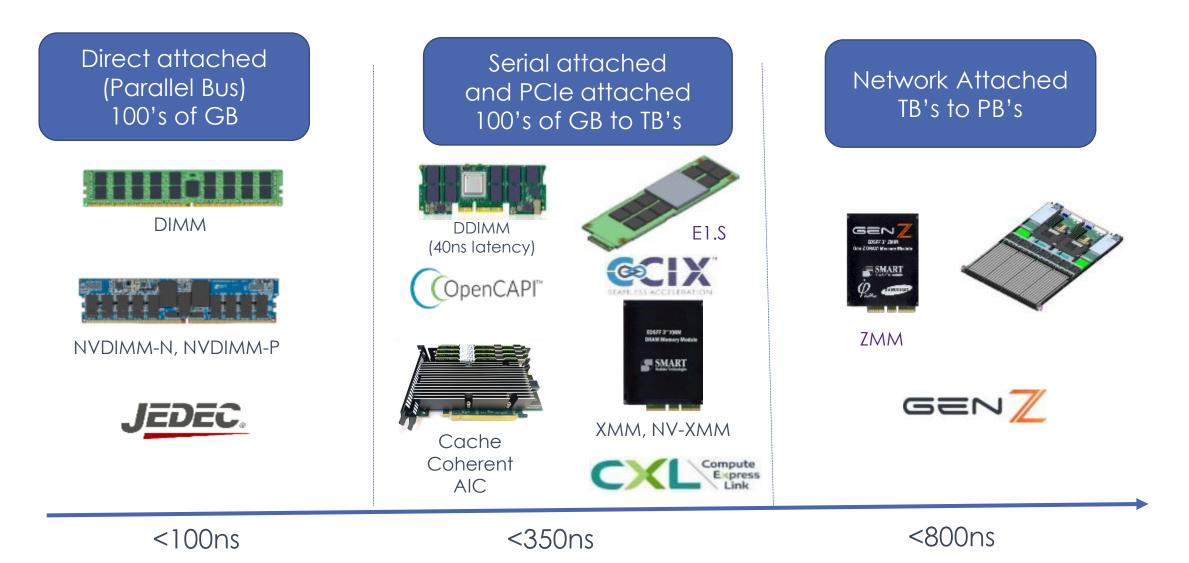

## **Form Factors**

Direct attached

Network Attached

|                     | (Parallel Bus)<br>100's of GB |                           | and PCIe at<br>100's of GB |                                                                |                                             | Network Attached<br>TB's to PB's |

|---------------------|-------------------------------|---------------------------|----------------------------|----------------------------------------------------------------|---------------------------------------------|----------------------------------|

|                     | DIMM                          | E1.S (×4)                 | E1.S (×8)                  | EDSFF 3* XMM<br>DRAM Memory Module<br>SMART<br>Redef Tribunger | E3.S (x8)                                   |                                  |

|                     | DDR4 DIMM                     | E1.S with x4<br>(1C)      | E1.S with x8 (2C)          | E3.S with x16<br>(4C)                                          | E3 with x8 (2C)                             | Network Card                     |

| Pins                | 288 pins<br>(64 data,         | 56 pins<br>(16 diff-data, | 84 pins<br>(32 diff-data,  | 140 pins<br>(64 diff-data,                                     | 84 pins                                     | Media and protocol               |

|                     | 87 sideband, rest<br>power)   | 16 sideband, 24<br>power) | 18 sideband, 34<br>power)  | 24 sideband, 52<br>power)                                      | (32 diff-data,<br>18 sideband,<br>34 power) | specific                         |

| Connect<br>or (LxW) | power)                        |                           | 18 sideband, 34            | 24 sideband, 52                                                | 18 sideband,                                | specific<br>SFP/QSFP/            |

Serial attached

# **Bandwidth**

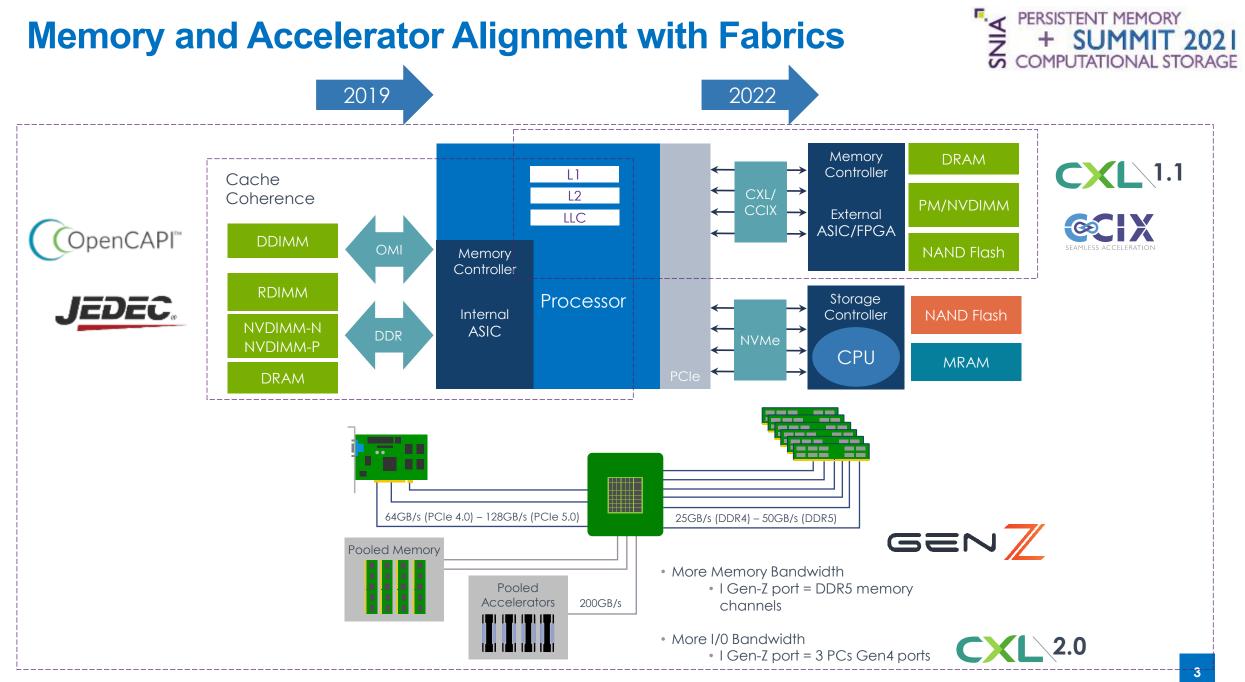

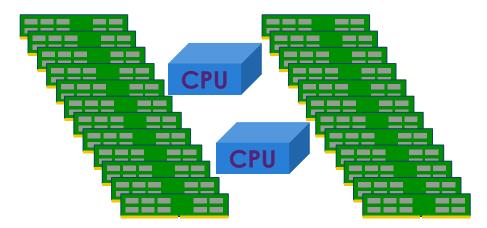

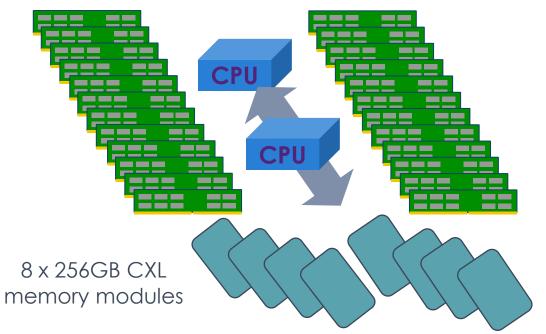

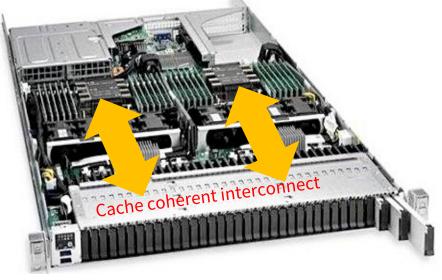

#### **Current Generation configuration**

Dual socket server with 64 core CPU and 12 x DDR4 channels populated with 128GB DDR4 DIMMs in 2 DIMMs/Channel

**Future Generation configuration – 2022** Dual socket server with **96 core CPU** and 12 x **DDR5** channels populated with 128GB DDR5 DIMMs in 2 DIMMs/Channel

- Total Memory = 3TB per server

- Theoretical maximum bandwidth of 614GB/s

- Bandwidth per core = 4.79GB/s

- Total Memory = 3TB (DDR5) + 2TB (CXL) per server

- Theoretical maximum bandwidth of 768GB/s (DDR5)+ 252GB/s (CXL)

- Bandwidth per core = 5.3GB/s (higher even with more CPU cores)

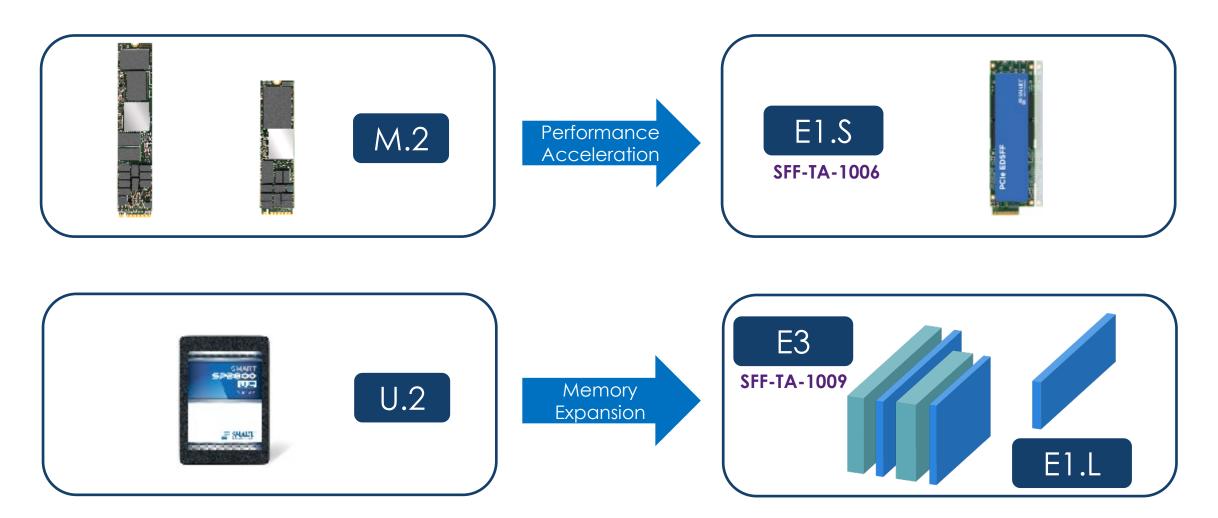

#### E1.S and E1.L for Memory Acceleration and Expansion

| PCIe EDSFF | - 199 <b>7</b> - 1997 | ine g |       |

|------------|-----------------------|-------|-------|

| q          |                       |       |       |

|            |                       | /譜/   | u 🔿 ' |

|            |                       |       | a 🔍 . |

| Feature                                                             | Description                                                                                                                                                                                                         |

|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host Interface                                                      | <ul> <li>Data: PCIe x4,x8</li> <li>Sideband: SMBus (I2C)</li> <li>Wake-up, Low-power (PWRDIS),</li> </ul>                                                                                                           |

| Memory                                                              | 64-128GB with DDR4 or DDR5                                                                                                                                                                                          |

| Protocols                                                           | NVMe, CXL, CCIX, Gen-Z                                                                                                                                                                                              |

| Power                                                               | <ul> <li>Multiple profiles from 12,16, 20, 25W</li> <li>Completely bus powered: 12V (main),<br/>3.3V Aux</li> <li>Supports low power modes (CLKREQ#,<br/>PWRDIS signaling)</li> </ul>                               |

| Targeted<br>Use Cases<br>Memory<br>Acceleration<br>and<br>Expansion | <ul> <li>Targeted for 1U Servers</li> <li>16 – 32 Slots per 1U Server</li> <li>Improves performance by offloading fixed functions like encryption, compression or Key-Value semantics to Memory modules.</li> </ul> |

### E3.S and E3.L for Memory Expansion

|   | EDSFF 3" XMM                |

|---|-----------------------------|

|   | DRAM Memory Module          |

|   | SMART                       |

|   | SMART<br>Noted Technologies |

|   |                             |

| 2 |                             |

| Feature                                      | Description                                                                                                                                                                    |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host Interface                               | <ul> <li>Data: PCIe x16</li> <li>Sideband: SMBus (I2C)</li> <li>Wake-up, Low-power (PWRDIS),</li> </ul>                                                                        |

| Memory                                       | Up to 256GB with DDR4 or DDR5<br>* Non-volatile persistent memory feature could<br>be support on this form-factor using back-up and<br>restore functionality like in NVDIMM-N. |

| Protocols                                    | NVMe, CXL, CCIX, Gen-Z                                                                                                                                                         |

| Power                                        | <ul> <li>2 profiles 25W (thin) and 40W (thick)</li> <li>Bus powered: 12V (main), 3.3V Aux</li> <li>Supports low power modes (CLKREQ#, PWRDIS signaling)</li> </ul>             |

| Targeted<br>Use Cases<br>Memory<br>Expansion | Targeted for 2U Server<br>Enables 4TB – 8 TB of Memory expansion with 16<br>E3.S modules in single 2U server, achieving better<br>throughput than direct attached DDR4 DIMM.   |

#### **OpenCAPI High Bandwidth Memory - DDIMM**

| Feature               | Description                                                                                                                                                                                                                                          |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host Interface        | • OpenCAPI                                                                                                                                                                                                                                           |

| Memory                | • Up to 256GB                                                                                                                                                                                                                                        |

| Protocols             | <ul> <li>OMI – Open Memory Interface</li> <li>The memory bus is defined with one read port and<br/>one write port per channel, each having eight<br/>unidirectional differential lanes</li> </ul>                                                    |

| Performance           | <ul> <li>DDR4-3200</li> <li>Latency 40ns</li> <li>Data throughput rate of 25.6GB/s with 8 lanes</li> <li>The DDIMM/OMI approach delivers up to 4TB of memory on a server at about 320GB/second or 512GB at up to 650GB/s sustained rates.</li> </ul> |

| Targeted<br>Use Cases | <ul> <li>Targeted for servers</li> <li>High bandwidth, low latency serial connection for<br/>memory, accelerators, network, storage, and other<br/>devices like ASICs</li> </ul>                                                                     |

### **NVDIMM for Persistent Memory**

#### Key Features of DDR4 and DDR5 NVDIMM-N

- Operation like DRAM

- Fast recovery from system power loss

- Software overhead can be eliminated

Backup Power

| Feature               | Description                                                                                                                                                                                                                                        |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host Interface        | • DDR                                                                                                                                                                                                                                              |

| Memory                | • DDR4 16GB, 32GB<br>• DDR5 32GB, 64GB                                                                                                                                                                                                             |

| Protocol              | • JEDEC Compliant DDR4 / DDR5                                                                                                                                                                                                                      |

| Features              | <ul> <li>Throughput of 25.6GB/s (DDR4)</li> <li>Latency ~20ns</li> <li>AES 256 bit Encryption</li> </ul>                                                                                                                                           |

| Targeted<br>Use Cases | <ul> <li>All Flash Arrays, Storage Servers, HPC,<br/>Al Training Servers</li> <li>Needed for very low latency tiering,<br/>caching, write buffering, metadata storage,<br/>checkpointing</li> <li>Needed for AI/ML algorithm processing</li> </ul> |

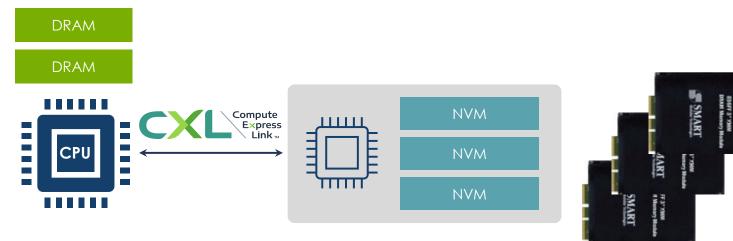

# **CXL-based NVDIMM (NV-XMM)**

Source: Modified from PIRL 2019, "Accelerate Everything", Stephen Bates, Eideticom

High-speed DRAM with built-in back-up power to back-up data to on-module Flash during power loss.

Source: PIRL 2019, "Accelerate Everything", Stephen Bates, Eideticom

# Conclusions

Future of Persistent Memory, DRAM and SSD Form Factors

# Thank you

Please visit snia.org/pm-summit for presentations

0

CIC EDSFE