FROM DATACENTER TO EDGE : VIRTUAL EVENT APRIL 21-22, 2021

# Compute Express Link™ (CXL™) 2.0 – Architecture and Benefits for Computational Storage

David Wang - Director, Memory Product Planning, Samsung Electronics

## **Industry Landscape**

## **CXL Consortium**

#### CXL Board of Directors

Open Industry Standard for **Cache Coherent Interconnect**

150+ Member Companies

### **CXL Delivers the Right Features & Architecture**

#### Challenges

Industry trends driving demand for faster data processing and next-gen data center performance

Increasing demand for heterogeneous computing and server disaggregation

Need for increased memory capacity and bandwidth

Standards-based interconnect with configuration flexibility for memory, storage, or accelerators

#### CXL

An open industrysupported cachecoherent

interconnect for

processors, memory

expansion and

accelerators

#### **Coherent Interface**

Leverages PCIe with 3 mixand-match protocols

#### Low Latency

.Cache and .Memory targeted at near CPU cache coherent latency

#### **Asymmetric Complexity**

Eases burdens of cache coherent interface designs

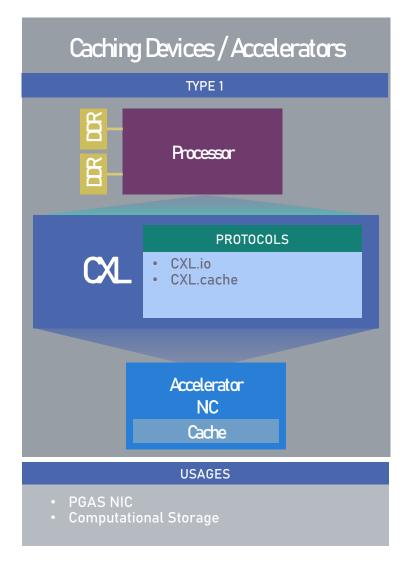

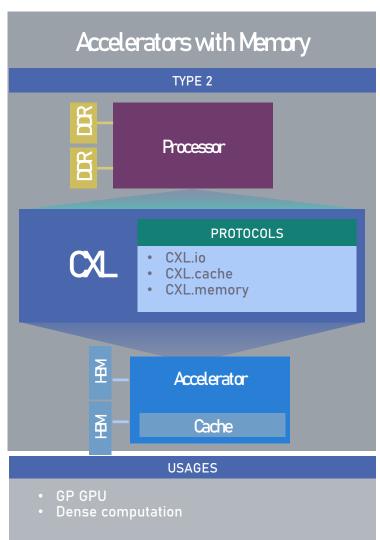

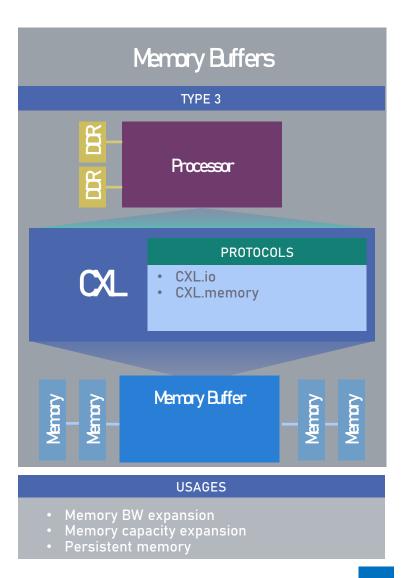

## Representative CXL Usages

## **CXL** and Computational Storage

|                                   |       |             |            |          |        |         |      |       |             |       |       |       |      |      |      |             |      |       |    |      |      |        |      |       |             |        |      |      |      |      |      |          |      |       |       |         |       | ٦.   |

|-----------------------------------|-------|-------------|------------|----------|--------|---------|------|-------|-------------|-------|-------|-------|------|------|------|-------------|------|-------|----|------|------|--------|------|-------|-------------|--------|------|------|------|------|------|----------|------|-------|-------|---------|-------|------|

| CXL                               |       | Flit Byte # |            |          |        |         |      |       |             |       |       |       |      |      |      |             | J١   |       |    |      |      |        |      |       |             |        |      |      |      |      |      |          |      |       |       |         |       |      |

| Cache                             | 0 1 2 | 3 4 5       | 6 7 8 9    | 10 1     | 1 12 1 | 13 14 1 | 5 16 | 17 18 | 8 19 3      | 20 21 | 22 23 | 24 2  | 5 26 | 27 2 | 8 29 | 30 31       | 32 : | 33 34 | 35 | 36 3 | 7 38 | 39 4   | 0 41 | 42 43 | 44 4        | 5 46 4 | 7 48 | 49 5 | 0 51 | 52 5 | 3 54 | 55 56    | 5 57 | 58 59 | 60 61 | 1 62 63 | 64 63 | 5    |

| Mem                               |       | Slot Byte # |            |          |        |         |      |       | Slot Byte # |       |       |       |      |      |      | Slot Byte # |      |       |    |      |      |        |      |       | Slot Byte # |        |      |      |      |      |      |          | ][   |       |       |         |       |      |

| Flit                              | 0 1 2 | 3 4 5       | 6 7 8 9    | 10 1     | 1 12 1 | 13 14 1 | 5 0  | 1 2   | 3           | 4 5   | 6 7   | 8 9   | 10   | 11 1 | 2 13 | 14 15       | 0    | 1 2   | 3  | 4 5  | 5 6  | 7 8    | 9    | 10 11 | 12 1        | 3 14 1 | 5 0  | 1 2  | 2 3  | 4    | 5 6  | 7 8      | 9    | 10 11 | 12 13 | 3 14 15 | 0 1   |      |

| 0<br>1<br>2<br># 3<br>4<br>5<br>6 |       |             | Data Chunk | <b>S</b> |        |         |      |       |             |       | Data  | Chunk |      |      |      |             |      |       |    |      | Di   | ata Ch | unk  |       |             |        |      |      |      |      | C    | lata Chi | unk  |       |       |         | CRC   | 0000 |

• Efficient (512b data + CRC) FLIT-based data movement

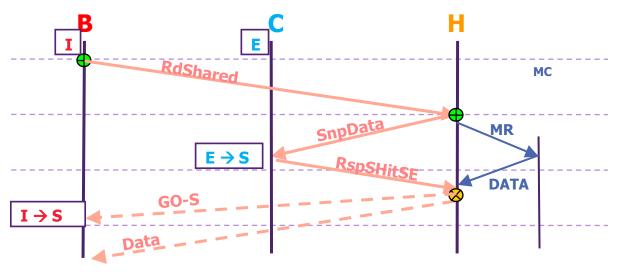

Host managed asymmetric coherence

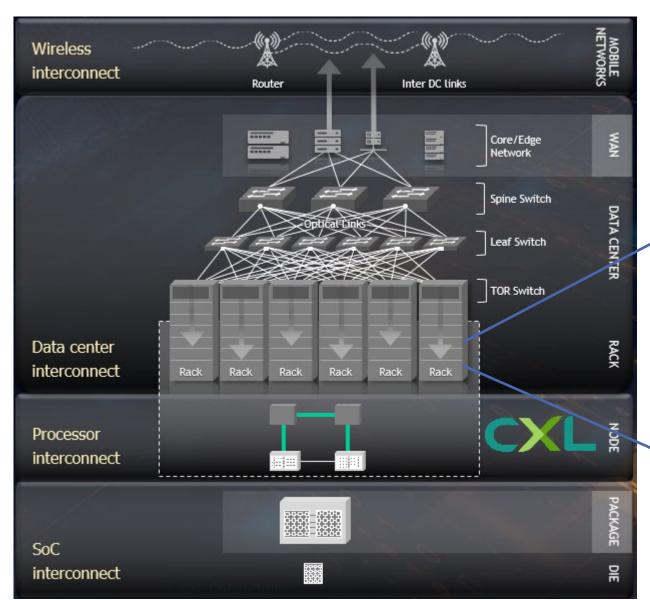

#### Data Center: Looking Outside in: Scope of CXL 2.0 over CXL 1.1

CXL 2.0 across Multiple Nodes inside a Rack/Chassis supporting pooling of resources

# **CXL 2.0 Scope: Hot-Plug, Persistence, Switching, and Dis-aggregation**

| Feature                                  | Description                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| CXL PCIe End-Point                       | CXL device to be discovered as PCIe Endpoint Support of CXL 1.1 devices directly connected to Root-Port or Downstream Switch Port                                                                                                                                                                      |  |  |  |  |  |  |  |

| Switching                                | Single level of switching with multiple Virtual Hierarchies (cascaded possible in a single hierarchy) CXL Memory Fan-Out & Pooling with Interleaving CXL.Cache is direct routed between CPU and device with a single caching device within a hierarchy. Downstream port must be capable of being PCIe. |  |  |  |  |  |  |  |

| Resource Pooling                         | Memory Pooling for Type3 device – Multiple Logical Device (MLD), a single device to be pooled across 16 Virtual Hierarchies.                                                                                                                                                                           |  |  |  |  |  |  |  |

| CXL.cache and<br>CXL.mem<br>enhancements | Persistence (Global Persistence Flush), Managed Hot-Plug, Function Level Reset Scope Clarification, Enhanced FLR for CXL Cache/Mem, Memory Error Reporting and QoS Telemetry                                                                                                                           |  |  |  |  |  |  |  |

| Security                                 | Authentication and Encryption – CXL.IO uses PCIe IDE, CXL defines similar capability for CXL.\$Mem                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Software<br>Infrastructure/ API          | ACPI & UEFI ECNs to cover notification and management of CXL Ports and devices CXL Switch API for a multi-host or memory pooled CXL switch configuration and management                                                                                                                                |  |  |  |  |  |  |  |

CXL 2.0 is <u>fully backwards compatible</u> with CXL 1.0/1.1 CXL 2.0 spec Rev 0.7 in Q1, 2020; Rev 0.9 in Q2, 2020, and CXL 2.0 in Q3, 2020 Predictable spec release cadence by CXL consortium to help the ecosystem plan better.

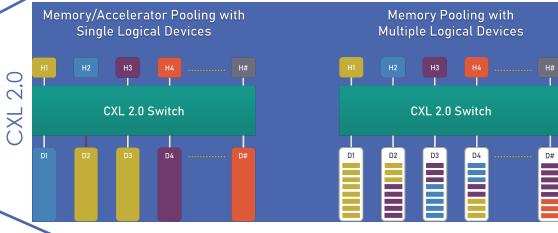

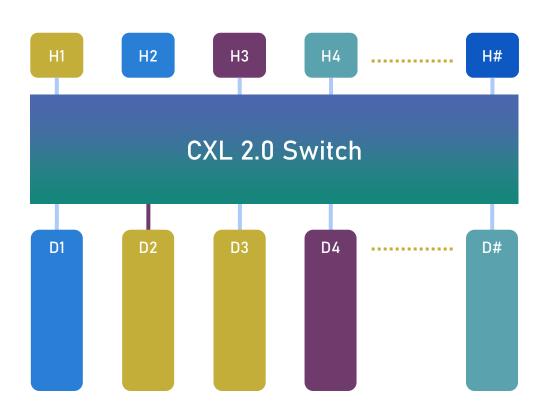

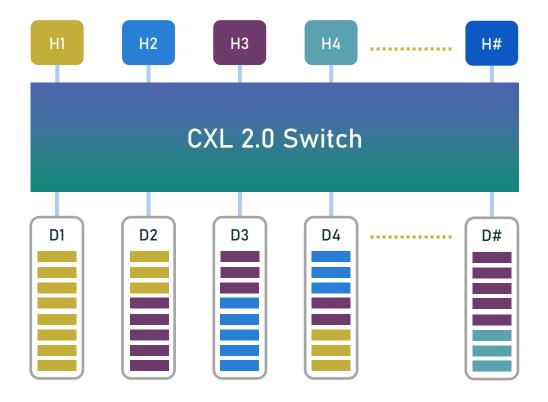

# Benefits of CXL 2.0 Switching Pooling

Memory/Accelerator Pooling with Single Logical Devices

Memory Pooling with Multiple Logical Devices

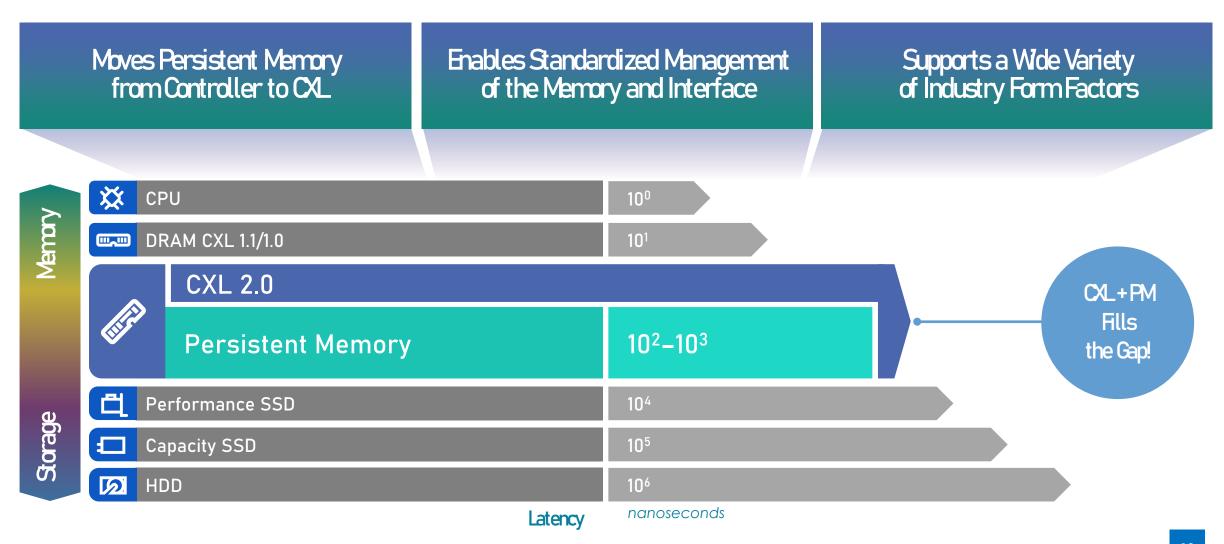

### **Benefits of CXL 2.0 and Persistent Memory**

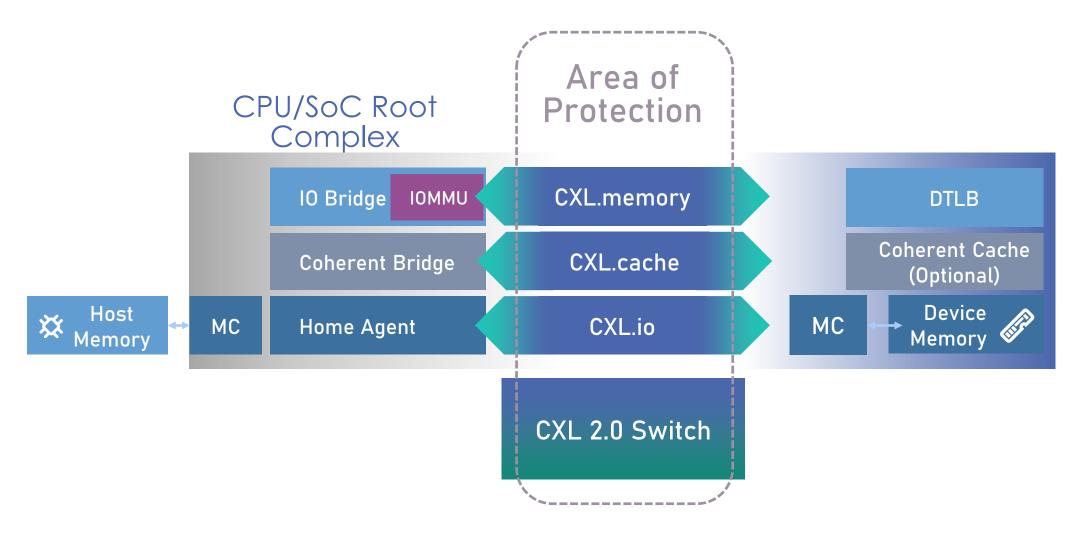

### **CXL 2.0 Security Benefits**

CXL 2.0 provides Integrity and Data Encryption of traffic across all entities (Root Complex, Switch, Device)

## **In Summary**

# CXL Consortium momentum continues to grow

- 150+ members and growing

- Responding to industry need and challenges

- Celebrating first anniversary of incorporation – second generation specification

- Responding to industry needs and challenges

## CXL20 introduces new features & usage models

- Switching, pooling, persistent memory support, security

- Fully backward compatible with CXL 1.1 and 1.0

- Built in Compliance & Interop program

& Interop program

#### Call to action

- Join CXL Consortium

- Visit <u>www.computeexpresslink.org</u> for more information

- Follow us on <u>Twitter</u> and <u>LinkedIn</u> for more updates!

## Thank you

Please visit <u>www.snia.org/pm-summit</u> for presentations