VIRTUAL EVENT • MAY 24-25, 2022

### Scaling NVDIMM-N Architecture for System Acceleration in DDR5 and CXL<sup>™</sup> - Enabled Systems

Presented by; Arthur Sainio and Pekon Gupta

# **Need for Persistent Memory**

#### Persistence

- System downtimes are costly but inevitable.

- To limit the blast radius, impacted services, VM or a downed server should be rebooted in the same state as it was earlier.

- Intermediate transaction states, configurations and metadata are saved in Persistent Memory even before transactions are fully committed.

- To identify the cause of failure, error logging until the latest event and security logging during a malicious hack are required.

- Persistence preserves event logs across power-cycles.

### Memory (low latency)

Layer 3 switch

er 3 switch

High latency may directly impact revenue or customer experience.

Cisco 3620

backborie

- Missed SLA like denial of transaction in credit card business means losing the transaction to your competitor or allowing fraudulent transaction.

- In High Frequency trading, A broker could lose millions, if their electronic trading platform is just few milliseconds behind the competition.

- Amazon found every 100ms of latency cost them 1% in sales.

- Google found an extra 0.5 seconds in search page generation time dropped traffic by 20%.

Source; The GigaSpaces Technologies Blog, Insights into In-Memory Computing and Real-time Analytics

# **Persistent Memory Solution Options**

COMPUTATIONAL STORAGE

|              | Volatile Memory with Backup Power (NVDIMM-N)                                                                                                                                                                                                                                         | Non-Volatile Media Based (NVDIMM-P)                                                                                                                                                                                          |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Architecture | power<br>lost?<br>NAND<br>Power<br>lost?<br>NAND<br>Power<br>lost?<br>Power<br>lost?                                                                                                                                                                                                 | MRAM Re-<br>RAM FRAM PCM* NRAM<br>Media<br>controller<br>J<br>J<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V                                                                         |

| Examples     | <ul> <li>NVDIMM-N</li> <li>CXL<sup>™</sup> NV-XMM implementations<br/>(Non-Volatile CXL Memory Modules)</li> </ul>                                                                                                                                                                   | <ul> <li>Intel Optane<sup>™</sup> PMem</li> <li>NVDIMM-P based implementations</li> <li>Different types of PM media</li> </ul>                                                                                               |

| Features     | <ul> <li>Low latency (RTT &lt; 50ns) (Incoming traffic hits DRAM)</li> <li>Granular Byte level addressing.</li> <li>High reliability (Flash used only during backup)</li> <li>Data retention for data at rest equivalent to NAND media.</li> <li>X Hold up power required</li> </ul> | <ul> <li>X Higher Latency</li> <li>✓ Granular Byte level addressing</li> <li>X Reliability (Limited by endurance of media)</li> <li>✓ Data retention across power-cycles</li> <li>✓ High density memory expansion</li> </ul> |

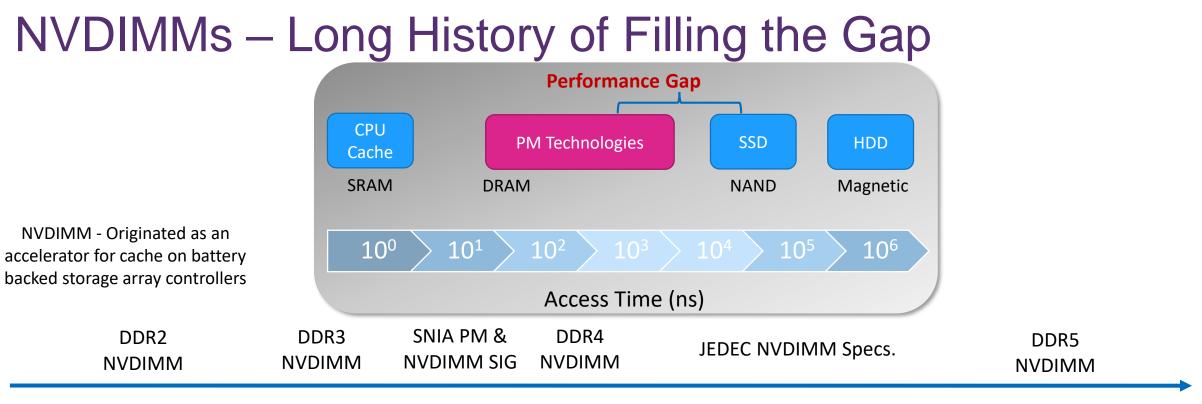

2007 2008 2010 2011 2012 2013 2014 2015 2016 2017 2018 2019 2020 2021 2022 2023

- Practical industry solution to dramatically increase system performance

- $\checkmark\,$  Provides direct access and removes IO and all the overhead

- $\checkmark\,$  Allows critical databases to be built in memory

- $\checkmark\,$  A memcached structure is faster than the any solid-state solution

- ✓ Uses off-the-shelf DRAM and Flash components

- $\checkmark\,$  NVDIMM solutions are widely adopted by flash storage array vendors.

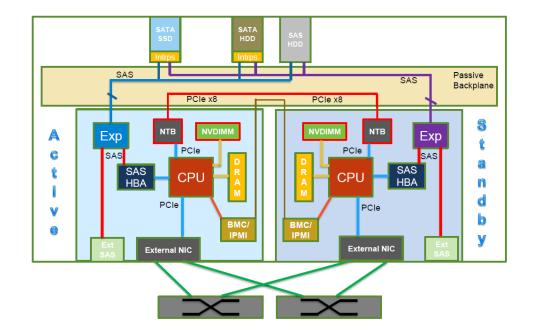

# Use Cases - NVDIMMs in Storage

#### As read cache

- The NVDIMM solution is low in complexity from a software and hardware implementation perspective.

- NVDIMMs cache hot data and metadata, thereby enabling performance with latencies in the sub-80ns range, almost 100x faster less than high end SSD available.

#### For Fault Tolerance

- Mirroring Data to and from NVDIMMs via PCIe NTB (Non-Transparent Bridging)

- NVDIMMs provide greater than 4X Write IOP latency improvement by reducing the time transient data must be replicated to the peer.

**Energy Backed Interface**

COMPUTATIONAL STORAGE

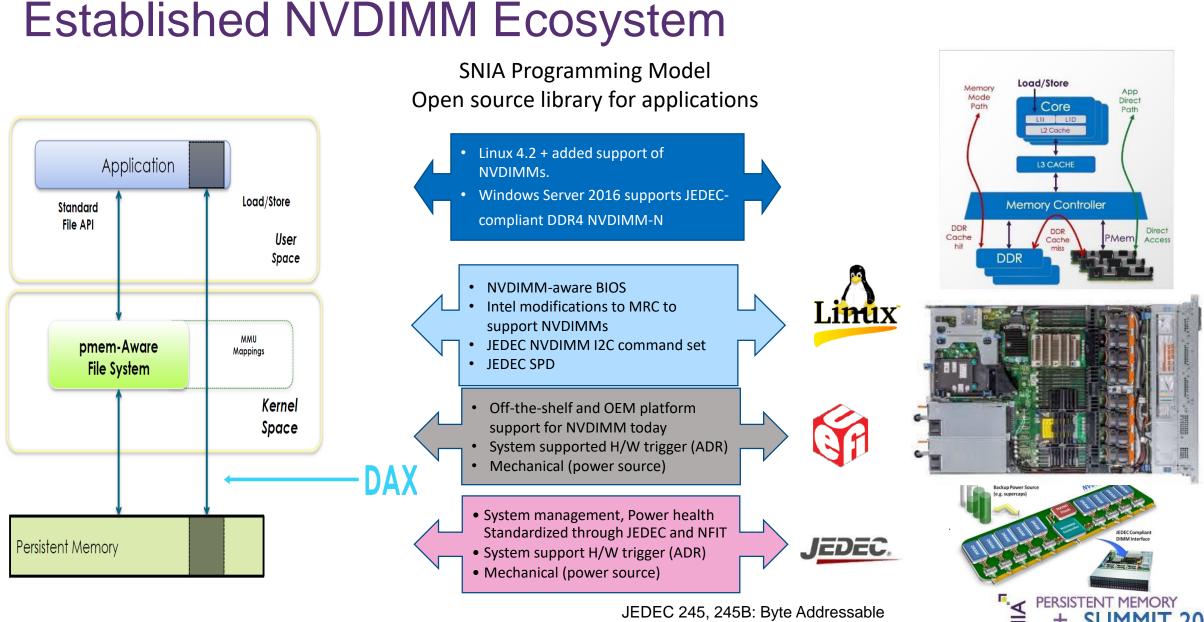

# NVDIMM Cookbook – Still Valid for DDR5 NVDIMM

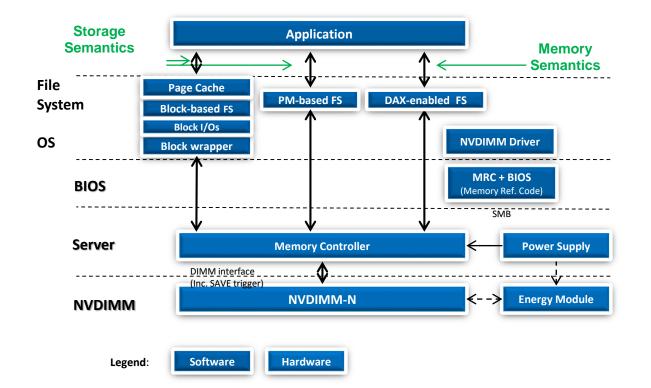

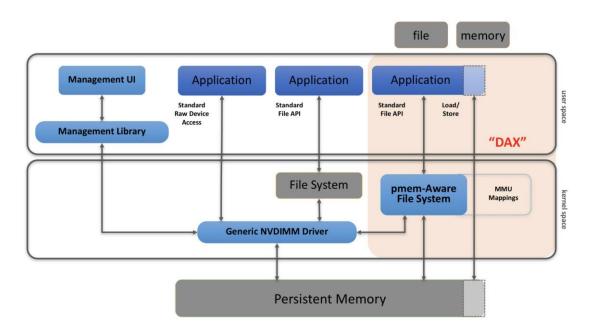

The ACPI NVDIMM Framework SNIA NVM Programming Model

# **NVDIMM Migration to DDR5**

| Technology              | DDR3                                                           | DDR4                                                          | DDR5                                                           | DDR5<br>Advantages                         |

|-------------------------|----------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------|

| Speed                   | 6.4 to 1.49 Mbps<br>data rate                                  | 1.6 to 3.2Gbps<br>data rate                                   | 4.8 to 6.4Gbps<br>data rate                                    | Higher Bandwidth. up to 6400<br>MHz        |

| IO Voltage              | 1.5V                                                           | 1.2V                                                          | 1.1V                                                           | Lower Power                                |

| Power<br>Management     | On Moth                                                        | er board                                                      | On DIMM (PMIC)                                                 | Better power efficiency and<br>scalability |

| Channel<br>Architecture | 72bit data channel<br>(64 data + 8 ECC)<br>2 channels per DIMM | 72bit data channel<br>(64 data + 8 ECC)<br>1 channel per DIMM | 40bit data channel<br>(32 data + 8 ECC)<br>2 channels per DIMM | Higher memory efficiency,<br>lower latency |

| Burst Length            | 4                                                              | 8                                                             | 16                                                             | Higher memory efficiency                   |

| Max. die density        | 8Gb                                                            | 16Gb                                                          | 32Gb                                                           | Higher capacity NVDIMMs                    |

| NVDIMM Types            | SODIMM, RDIMM                                                  | RDIMM                                                         | LRDIMM, RDIMM                                                  | Same form factor                           |

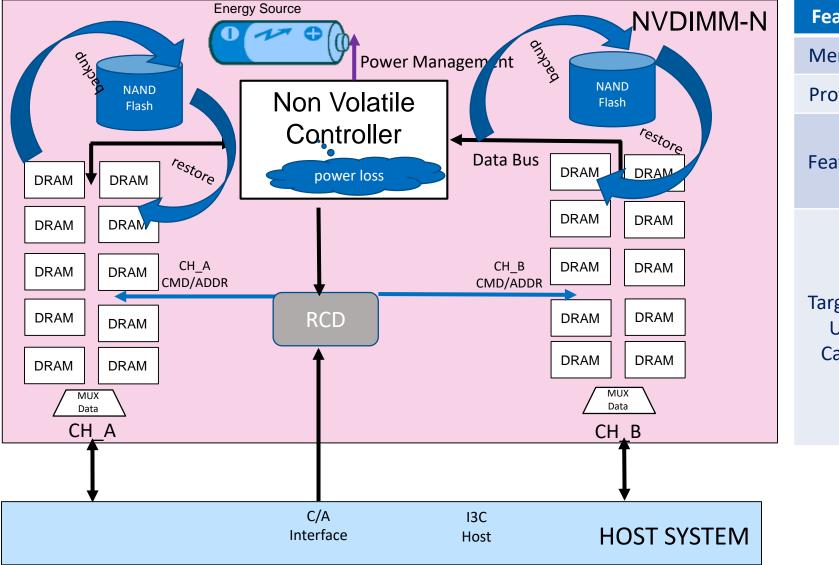

# **DDR5 NVDIMM Architecture**

| eature                  | Description                                                                                                                                                                                                                                                |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lemory                  | • DDR5-4800 32GB / 64GB                                                                                                                                                                                                                                    |

| rotocol                 | JEDEC Compliant DDR5                                                                                                                                                                                                                                       |

| eatures                 | <ul> <li>Throughput of 63.0 GB/s</li> <li>Latency ~20ns</li> <li>AES 256 bit Encryption</li> </ul>                                                                                                                                                         |

| argeted<br>Use<br>Cases | <ul> <li>All Flash Arrays, Storage Servers,<br/>HPC,<br/>Al Training Servers</li> <li>Needed for very low latency tiering,<br/>caching, write buffering, metadata<br/>storage, checkpointing</li> <li>Needed for Al/ML algorithm<br/>processing</li> </ul> |

|                         | processing                                                                                                                                                                                                                                                 |

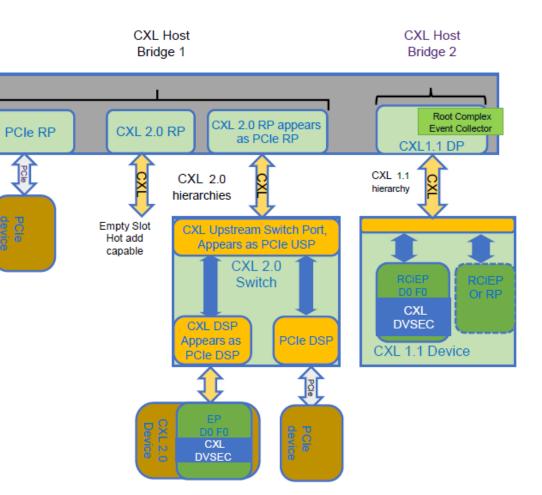

# CXL 2.0 Support for Persistent Memory

## PCIe enumeration

- NFIT not used for CXL

- Leverage PCIe framework

- MMIO registers

- Mailbox interface, etc.

- Command Interface

- Minor changes to external specs like ACPI/UEFI

Source; SNIA PM Summit Andy Rudoff April 2021

# CXL 2.0 Support for Persistent Memory

- Operate with standard CXL type 3 Linux and Windows memory driver for enumeration, configuration, I/O, and management.

- DRAM equivalent latency and endurance; Endurance limited only by Save/Restore cycles to NV

- Architecture supports multiple form factors

- End-to-End data protection from CXL host through Memory Buffer, NVC, and on all storage devices.

- NV data at rest must be encrypted.

- Support on module (device managed) or off module (host managed) NV Save energy source.

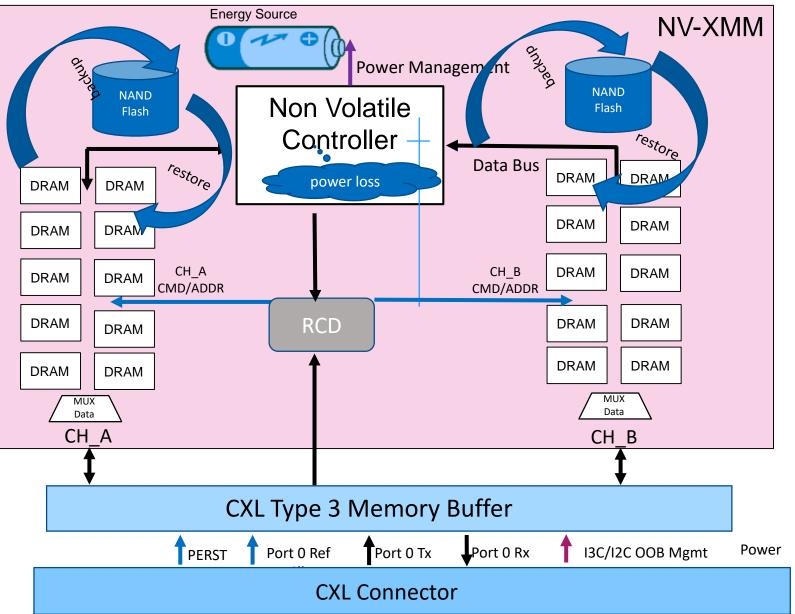

# CXL<sup>™</sup>-based Persistent Memory - NV-XMM

## CXL Type 3 PM (NV-XMM) Design Goals:

- On board power source for back-up power

- Self managed back-up and restore

- Standard Programming model for CXL Type-3 devices

- DRAM equivalent latency and endurance;

- Unlimited Endurance as active data writes directly go to DRAM

- Encrypting data during back-up.

## CXL Type 3 PM (NV-XMM)

- Memory Buffer to be used with RCD.

- Infrequent Save/Restore cycles (< 10 per day)</p>

- Form Factors

- E3.S / AIC / E1.S

## CXL<sup>™</sup> NV-XMM Architecture

| Feature                  | Description                                                                                                                                                                                                                                                         |  |  |  |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Memory                   | • DDR5                                                                                                                                                                                                                                                              |  |  |  |

| Protocol                 | • CXL 2.0                                                                                                                                                                                                                                                           |  |  |  |

| Form<br>Factors          | • E3.S 2T, AIC                                                                                                                                                                                                                                                      |  |  |  |

| Features                 | <ul> <li>Unlimited endurance</li> <li>Latency &lt;100ns</li> <li>Secure backup</li> </ul>                                                                                                                                                                           |  |  |  |

| Targeted<br>Use<br>Cases | <ul> <li>All Flash Arrays, Storage Servers,</li> <li>HPC, AI Training Servers</li> <li>For very low latency tiering,<br/>caching, write buffering, metadata<br/>storage, checkpointing</li> <li>For AI/ML algorithm processing</li> <li>New applications</li> </ul> |  |  |  |

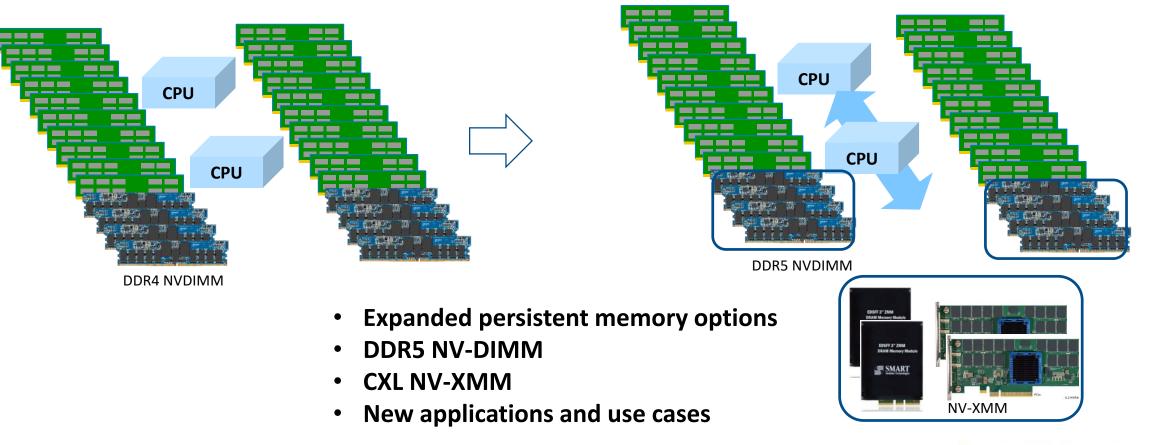

# CXL<sup>™</sup> Adds Capacity, Bandwidth and Persistent Memory

Current Gen Systems DDR4 NVDIMM-N Next Gen Systems DDR5 NVDIMM-N and CXL NV-XMM

## Key Takeaways

- NVDIMM-N architecture transition from DDR4 to DDR5 without significant changes.

- Any latency-sensitive data that is continuously changing can benefit from NVDIMM and NV-XMM.

- DDR5 NVDMM-N is near-term and will fill a gap for high performance, low latency persistent memory applications.

- CXL NV-XMM will follow and also be used for low latency-sensitive applications.

- CXL NV-XMM will coexist with DDR5 NVDIMM-N

- CXL NV-XMM will open up new use cases for higher capacity and composability

# Please take a moment to rate this session.

Your feedback is important to us.