# THE SOLID STATE TRANSFORMATION OF THE DATA CENTER

Amber Huffman

Intel Fellow, Data Center Group, Intel Corporation

President, NVM Express, Inc.

September 26, 2018

### **Notices & Disclaimers**

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. **No product can be absolutely secure.**

Tests document performance of components on a particular test, in specific systems. Differences in hardware, software, or configuration will affect actual performance. For more complete information about performance and benchmark results, visit <a href="http://www.intel.com/benchmarks">http://www.intel.com/benchmarks</a>.

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products. For more complete information visit <a href="http://www.intel.com/benchmarks">http://www.intel.com/benchmarks</a>.

Intel's compilers may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include SSE2, SSE3, and SSSE3 instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors. Certain optimizations not specific to Intel microarchitecture are reserved for Intel microprocessors. Please refer to the applicable product User and Reference Guides for more information regarding the specific instruction sets covered by this notice.

The benchmark results may need to be revised as additional testing is conducted. The results depend on the specific platform configurations and workloads utilized in the testing, and may not be applicable to any particular user's components, computer system or workloads. The results are not necessarily representative of other benchmarks and other benchmark results may show greater or lesser impact from mitigations.

Intel does not control or audit third-party benchmark data or the web sites referenced in this document. You should visit the referenced web site and confirm whether referenced data are accurate.

© 2018 Intel Corporation.

Intel, the Intel logo, and Intel Xeon are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as property of others.

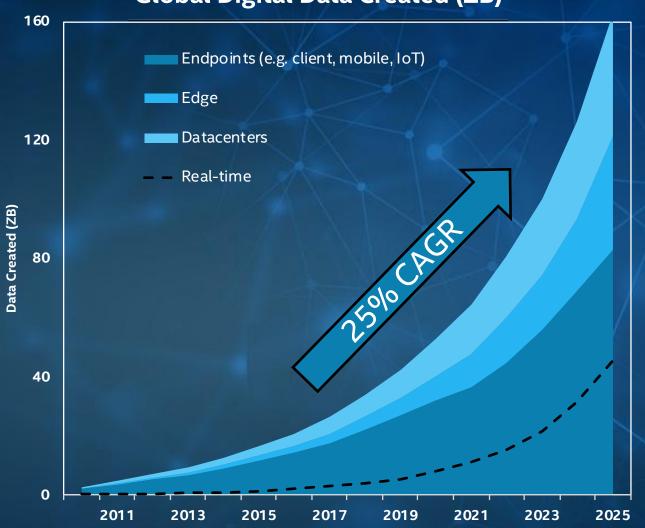

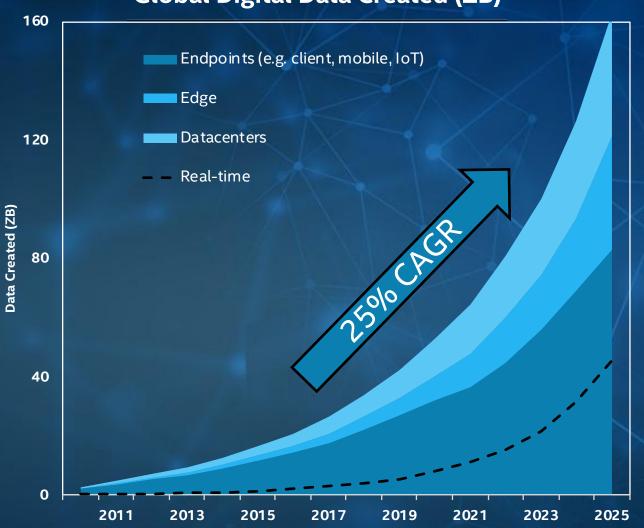

# **ZETABYTES AND MORE ZETABYTES...**

### Global Digital Data Created (ZB)

# TODAY'S TALK

1. OUR INDUSTRY TRANSFORMATION TO EMBRACE NVM

2. OUR CONTINUED OPPORTUNITIES TOGETHER

# THE JOURNEY BEGINS ~ 2000

# **ROLL BACK A DECADE+**

Intel Developer Forum 2007

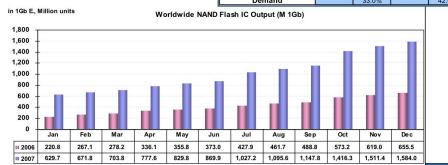

### DRAMeXchange Projects SSD to Become the New Killer Application of NAND Flash in 2008

Tuesday, January 09, 2007 DRAMeXchange

SanDisk, who is a prominent Flash memory card maker, unveiled a 1.8j 32Gb Solid State Drive (SSD) storage device on January 4th, 2007. The product is initially expected to target enterprises. As the unit production costs for NAND Flash are expected to drop further, SanDisk expects the general public (especially business executives who travel frequently) to begin showing interest in purchasing NBs that are equipped with an SSD in the near future.

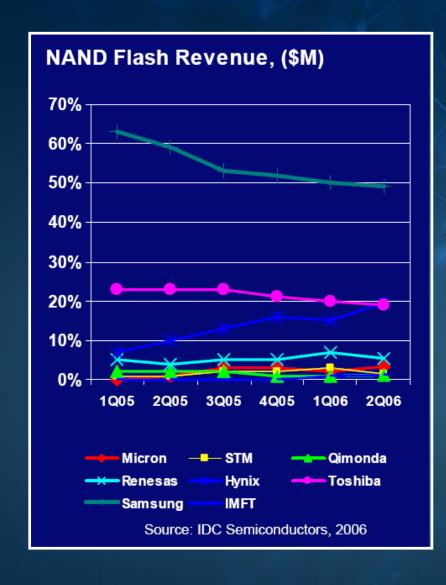

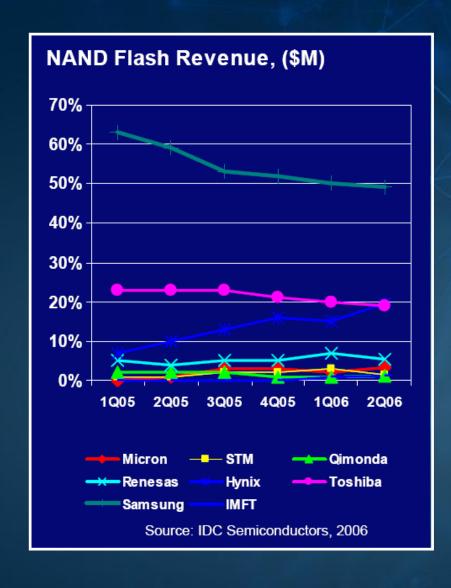

### PC is a Driver of NAND Growth

- NAND growth is projected to be 140% YoY for 06/07

- Largest growth area is "Others"

> 50% projected QoQ growth for Q3/Q4

- A key component of the "Others" category is PC uses

| Unit: in 1Gb E., Million unit | Q30      | )7F     | Q407F         |         |  |

|-------------------------------|----------|---------|---------------|---------|--|

|                               | Shipment | Demand  | Shipment      | Demand  |  |

| Digital Still Cameras         | 26.8     | 697.9   | 31.5          | 884.6   |  |

| Digital Still Callieras       | 13.7%    | 32.0%   | 17.4%         | 27.0%   |  |

| Cell phones                   | 271.7    | 880.2   | 309.7         | 1,271.5 |  |

| Cell phones                   | 7.0%     | 38.0%   | 14.0%         | 44.0%   |  |

| USB Drives                    | 35.1     | 615.2   | 38.9          | 734.5   |  |

| USB Drives                    | 14.8%    | 29.0%   | 38.9<br>10.7% | 19.0%   |  |

| Flash-based MP3/PMP           | 32.6     | 779.7   | 46.7          | 1,223.4 |  |

| Flash-based WP3/PWP           | 9.5%     | 32.0%   | 43.3%         | 57.0%   |  |

| Other                         |          | 250 8   |               | 570.9   |  |

| (DVs · Game                   |          | 54.0%   |               | 61.0%   |  |

| Total NAND Flash              | L        | 0,000.0 |               | 7,000.0 |  |

| Demand                        |          | 33.0%   |               | 42.0%   |  |

Intel Developer FORUM

Source: DRAMeXchange, 4/2007

(intel)

It was a <u>question</u> if SSDs would be a killer application for NAND.

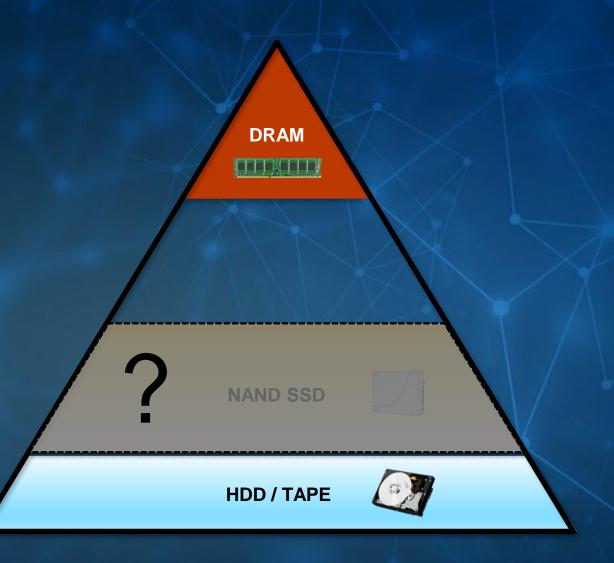

# NAND SSD TIER?

# THE NEED FOR OPEN NAND FLASH INTERFACE

# NO STANDARD NAND INTERFACE

There were many vendors, yet no standard interface, making it difficult to design SSDs.

# ENTER OPEN NAND FLASH INTERFACE (ONFI)

EE Times: Semi News

Intel, Hynix, Micron, Sony form NAND group

Mark LaPedus

- mines

(05/09/2006 4:24 PM EST)

PRINT THIS STORY

SEND AS EMAIL

REPRINTS

SAN JOSE, Calif. — Seeking to accelerate the time-to-market for NAND-based flash memories in the marketplace, Hynix, Intel, Micron, Phison and Sony are among the founding companies that on Tuesday (May 9) announced the formation of a new and long-awaited working group in the arena.

Open NAND Flash Interface Specification

Revision 1.0 28-December-2006

Hynix Semiconductor Intel Corporation Micron Technology, Inc. Phison Electronics Corp. Sony Corporation STMicroelectronics

ONFI codified commonalities, and then started to scale for SSDs.

# INCREASING PERFORMANCE FOR SSDS

Intel Developer Forum 2008

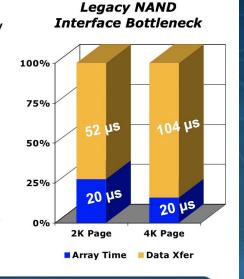

### **Legacy Interface Bottleneck**

- NAND performance is determined by two elements

- NAND array access time

- Data transfer time across the bus

- For legacy NAND reads, the dominant factor is the bus!

- Performance is limited to 40 MB/s

- With interface improvements data could be read at over 150 MB/s

- The issue gets <u>significantly worse</u> as page size increases

80+ μs "hiccup" waiting for the interface bottleneck during every 4KB read.

Intel Developer FORUM

### **ONFi 2.0 Eliminates the Bottleneck**

- ONFi 2.0 was published in February

- Adds a synchronous DDR interface option for high speed

- 133 MT/s in first generation

- Scalability to 400 MT/s

- 3.3V and 1.8V VccQ options

- Optimized BGA package

- Additional headroom found, ONFi 2.1 underway now and will add 166 MT/s and 200 MT/s speeds

| Interface Roadmap |                       |  |  |  |

|-------------------|-----------------------|--|--|--|

| Legacy            | <b>Legacy</b> 40 MB/s |  |  |  |

| Gen1              | ~ 133 MB/s            |  |  |  |

| Gen2              | ~ 266 MB/s            |  |  |  |

| Gen3              | 400 MB/s +            |  |  |  |

ONFi 2.0 triples the legacy interface speed.

ONFi 2.1 with more speed targeted for 2H'08.

Intel Developer FORUM

11

ONFI defined 10x scaling of NAND interface in < 2 years.

# **ENABLING SCALE FOR SSD INDUSTRY**

### **JEDEC and ONFi Collaboration**

- The ONFi Workgroup is pleased to team up with JEDEC on NAND standardization moving forward

- ONFi is submitting the ONFi 2.0 specification as part of the joint effort

ONFI / JEDEC collaboration enabled unifying the industry to support scale of SSD ambitions.

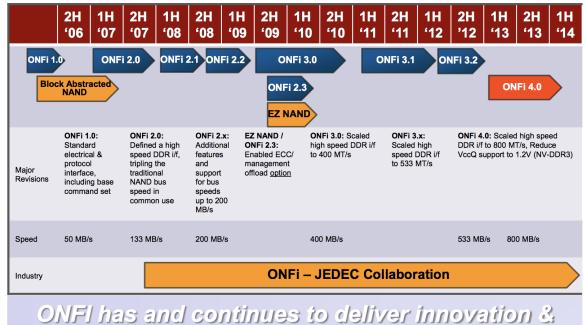

# ONFI CONTINUED INNOVATION

### Flash Memory Summit 2014

# ONFI Workgroup Continues To Produce Results!

ONFI has and continues to deliver innovation & interoperability enabling faster NAND adoption

Steady innovation...

# **KEEPING PACE WITH SSD NEEDS**

**Open NAND Flash Interface Specification**

Intel Corporation

Micron Technology, Inc.

Phison Electronics Corp.

Western Digital Corporation

SK Hynix, Inc.

Sony Corporation

ONFI 4.0 in 2014 scaled to 800 MT/s.

ONFI 4.1 in 2017 scaled to 1200 MT/s.

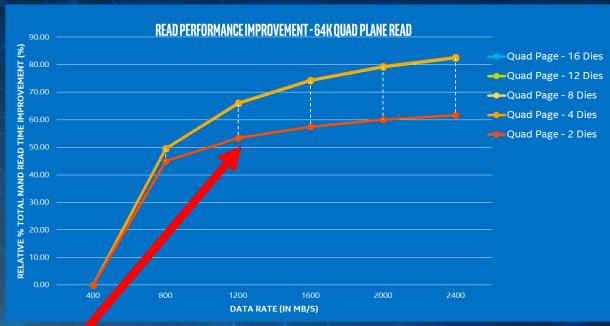

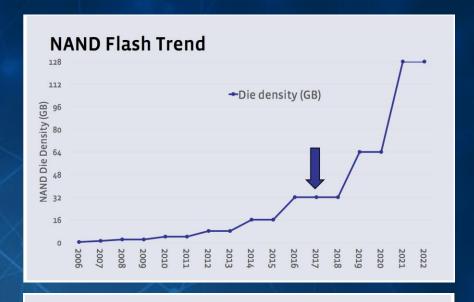

# NAND PERFORMANCE IMPROVEMENTS ARE SLOWING

ROI reduction at higher transfer rates due to NAND performance. Keep ONFI steady, <u>unless</u> breakthrough in NAND media.

# THE PATH TO NVM EXPRESS

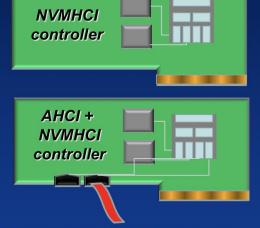

# THE ORIGINAL "NVMHCI"

### Flash Memory Summit 2009

## Remember NVMHCI: An Optimized Interface for NVM

- NVMHCI: Non-Volatile Memory Host Controller Interface

- NVMHCI is a clean and optimized interface for SSDs and caches

- NVM equivalent of the SATA AHCI controller interface

Santa Clara, CA US August 2009

\*Other names and brands may be claimed as the property of others

### Technical Essence of NVMHCI

- NVMHCI defines a standard programming interface for non-volatile memory subsystems

- Leverage AHCI to provide best infrastructure for caching

- One driver for HDDs and NAND

- Allows NVMHCI registers to appear as:

- A separate PCI device

- · A port within an existing AHCl controller

- NVMHCI is a logical interface

- All NAND management abstracted out: NAND technology changes too quickly

- All caching algorithms are outside the spec: NVMHCI only defines how caching software gets access to the NAND

- Optimized interface for both cache and SSD usage models

Santa Clara, CA USA Nugust 2009

# NVMHCI FOR CLIENT WAS A MISFIRE

# NVMHCI AS A SPRING BOARD FOR ENTERPRISE

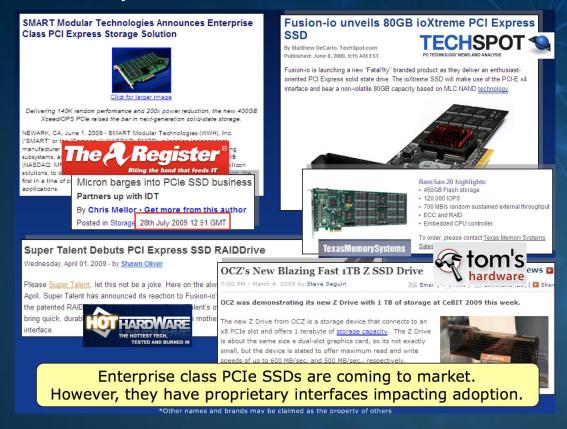

### Flash Memory Summit 2009

# Extend NVMHCI for Enterprise class PCIe SSDs

- Extend NVMHCI to meet the needs of Enterprise PCIe SSDs

- · Address Enterprise server scenarios

- Enables SSD vendors to focus on building a great SSD

- Enables OS vendors to deliver a great driver for all PCle SSDs

- Enables OEMs to qualify a single driver on each OS, with features implemented in a consistent fashion, reducing time to market

- Leverage NVMHCI interface, software infrastructure, and Workgroup to fill this gap quickly with a streamlined solution

- Make NVMHCI an ideal interface for Enterprise PCIe SSDs

- Take advantage of drivers already written or underway

- Take advantage of existing Workgroup, an efficient team that can execute quickly

Santa Clara, CA USA August 2009

11

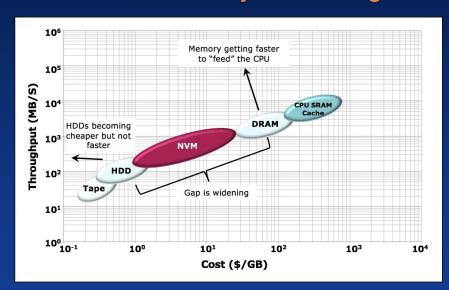

# ADDRESSING THE GAP ....

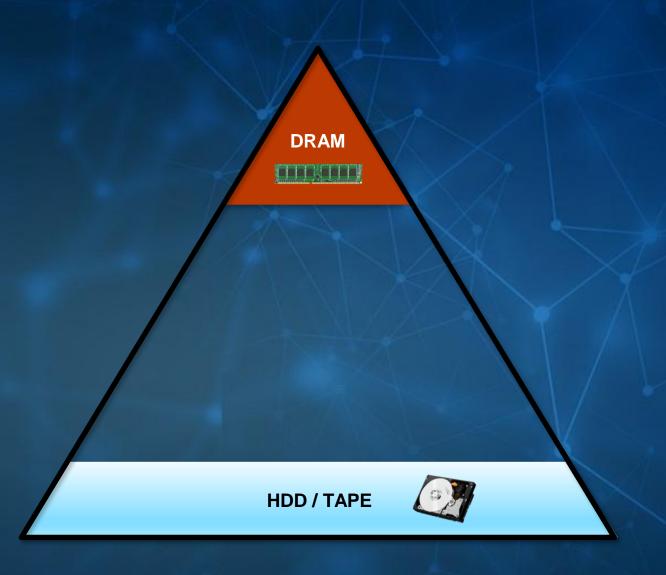

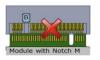

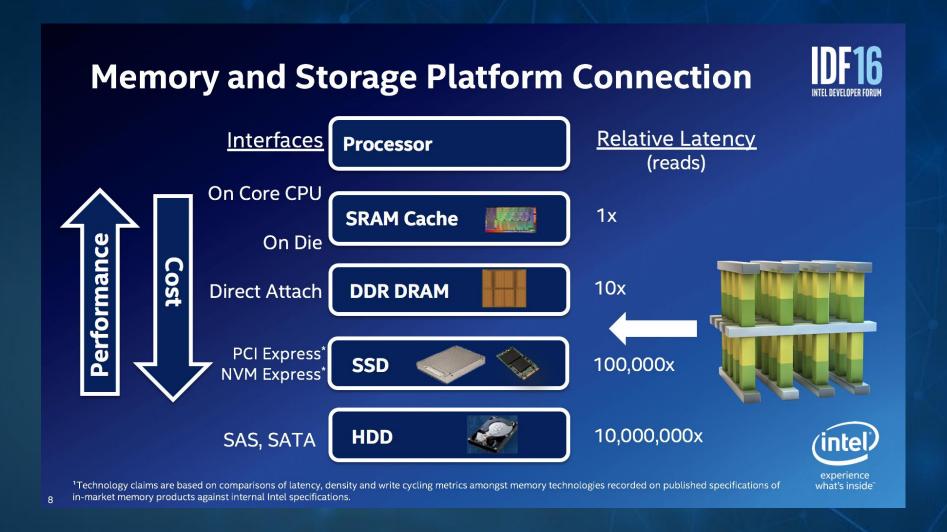

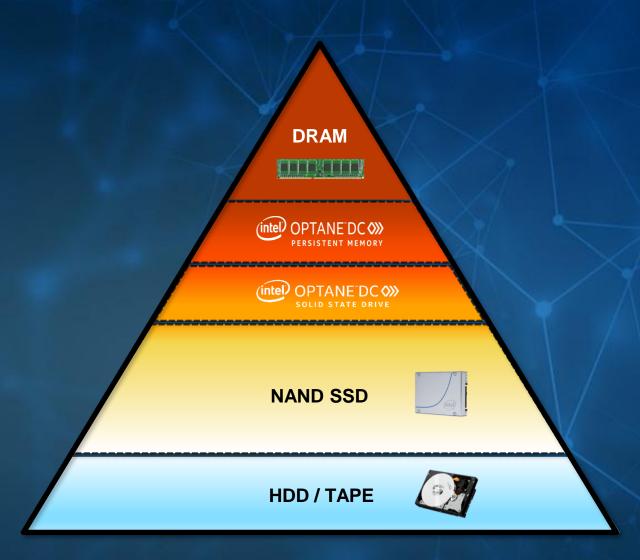

# Gap in the Storage/Memory Hierarchy is Growing

NVM is filling the price/performance gap between DRAM and HDD, thereby creating the "I/O Memory Tier"

August 2010

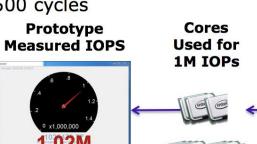

# Enterprise NVMHCI Goals & Timeline

- Goals for standard:

- Address Enterprise usage scenarios

- Enable an efficient & scalable interface, from very high-end to client

- Ensure no interface impediments to exceeding > 1M IOPs

- Enable OS vendors to deliver standard high performance drivers

- Provide a consistent feature set to enable SSD interoperability

- Reduce TTM for PCIe SSDs by enabling OEMs to validate/qual one PCIe SSD driver for each OS and one consistent feature set

- To get involved, join the NVMHCI Workgroup

- Details at http://www.intel.com/standards/nvmhci

|            | Apr<br>'10 | May<br>'10                      | Jun<br>'10 | Jul<br>'10 | Aug<br>'10                            | Sep<br>'10 | Oct<br>'10 | Nov<br>'10                        | Dec<br>'10 |

|------------|------------|---------------------------------|------------|------------|---------------------------------------|------------|------------|-----------------------------------|------------|

| Revision   | 0.5        |                                 |            |            | 0.7                                   | •          | 0.9        | RC                                | 1.0        |

| Definition |            | asic<br>lities and<br>ach defin |            | comple     | asic defir<br>ete for al<br>es. Feati | l          | RC: M      | ratum or<br>ember re<br>iblished. | eview.     |

0.70 revision achieved, available for Contributor review. Schedule enables product intercept in 2012.

Flash Memory Summit 2010

# **PRINCIPLES OF ENTERPRISE NVMHCI**

for now & the future.

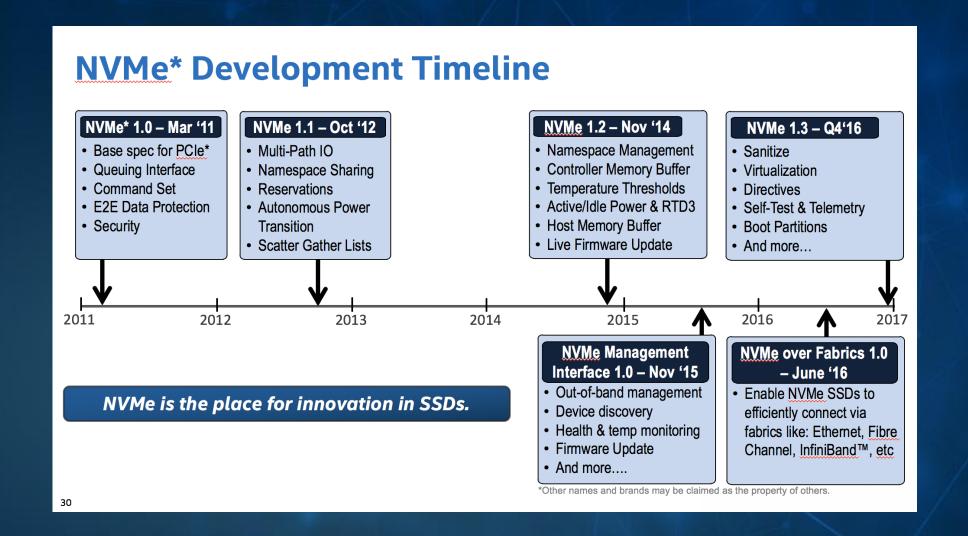

# **NVM EXPRESS "BORN" IN MARCH 2011**

### NVM Express\* Overview **TVM**

- NVM Express is a scalable host controller interface designed for Enterprise and Client systems that use PCI Express\* SSDs

- Includes optimized register interface and command set

- NVMe was developed by industry consortium of 80+ members and is directed by a 10 company Promoter Group

NVMe 1.0 published on March 1<sup>st</sup>, available at nvmexpress.org

NVMe standardization effort is complete & stable Product introductions coming in 2012

### **NVMe\*: Efficient SSD Performance**

|                                                                     | AHCI¹                                                       | <b>NVM</b><br>EXPRESS                      |

|---------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------|

| Uncacheable Register Reads Each consumes 2000 CPU cycles            | 4 per command<br>8000 cycles, ~ 2.5 μs                      | <b>0</b> per command                       |

| MSI-X and Interrupt Steering Ensures one core not IOPs bottleneck   | No                                                          | Yes                                        |

| Parallelism & Multiple Threads Ensures one core not IOPs bottleneck | Requires synchronization lock to issue command              | No locking, doorbell<br>register per Queue |

| Maximum Queue Depth Ensures one core not IOPs bottleneck            | 32                                                          | 64K Queues<br>64K Commands per Q           |

| Efficiency for 4KB Commands 4KB critical in Client and Enterprise   | Command parameters require two serialized host DRAM fetches | Command parameters in one 64B fetch        |

NVMe designed for high parallelism and low latency

O AHCI: Serial ATA programming interface. See http://www.intel.com/technology/serialata/ahci.htm

# DEVELOPING THE **ECOSYSTEM**

**InterOperability**

Laboratory

### Intel Developer Forum 2012

### **Interoperability Program Underway**

• The NVM Express Workgroup is collaborating with an industry leader, UNH-IOL, to develop the NVMe Interoperability program

March 12, 2012 08:00 AM Eastern Daylight Time

Industry Leaders Develop New, High-Performance PCIe SSD Solutions at UNH-IOL

Lab Now Accepting Founding Member Companies for NVMe Consortium

DURHAM, N.H.-(GUSINESS WIRE)—The University of New Hampshire InterOperability Laboratory (UNH-IOL), an independent provider of broad-based testing and standards conformance services for the networking and storage industries, is accepting founding members for the laboratory's new Non-Volatile Memory Express (NVMe) Consortium. The NVMe Consortium will focus on developing an interoperability test suite for NVMe compilant software and devices. Founding members will join industry leaders Deli, EMC, IDT, Intel, LSI Corporation, NetApp, Oracle and SanDisk to create new, innovative, high-performance storage solutions based on the NVMe standard for PCIe SSDs.

- UNH-IOL has extensive experience in conformance and interop test services for leading industry standards in storage & networking (SATA, SAS, <u>Fibre</u> Channel, etc.)

- Since late 2011 UNH-IOL has been working with the <u>NVMe</u>

Promoter Group to develop <u>NVMe</u> test documentation and tools

NVMe is working with UNH-IOL to ensure an interoperable ecosystem that OEMs can count on

NVMe = NVM Express

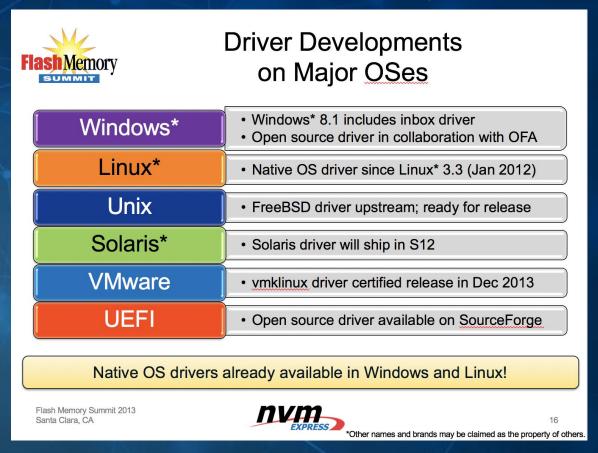

### Flash Memory Summit 2013

# BUILDING OUT ENTERPRISE FEATURES

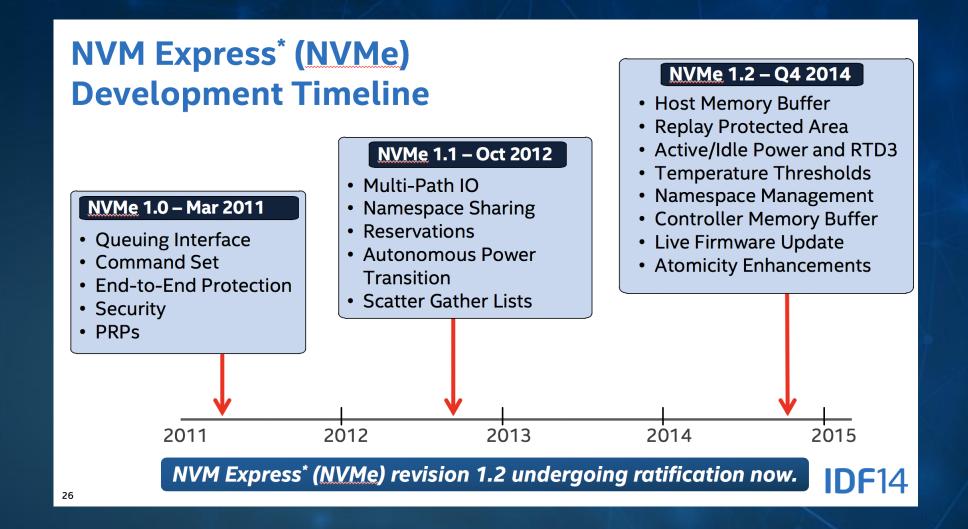

### **NVM Express\* 1.1 Overview**

• The NVM Express 1.1 specification, published in October of 2012, adds additional optional client and Enterprise features

### Multi-path Support

- Reservations

- Unique Identifier per Namespace

- Subsystem Reset

### **Power Optimizations**

**Autonomous Power State Transitions**

### Command Enhancements

- Scatter Gather List support

- Active Namespace Reporting

- Persistent Features Across **Power States**

- Write Zeros Command

**IDF**13

### **Multi-path Support**

- Multi-path includes the traditional dual port model

- With PCI Express\*, it extends further with switches

- In some multi-host environments, like Windows\* clusters, reservations may be used to coordinate host access

- NVMe 1.1 includes a simplified reservations mechanism that is compatible with implementations that use SCSI reservations

- · What is a reservation? Enables two or more hosts to coordinate access to a shared namespace.

- A reservation may allow Host A and Host B access, but disallow Host C

**IDF**13

# NVME SHIPS IN 2H 2013

### **NVM Express\* Deployment is Starting**

- First plugfest held May 2013 with 11 companies participating

- Three devices on Integrator's List

- Next plugfest planned for Q4

- Samsung announced first NVM Express\* (NVMe) product in July

FOR IMMEDIATE RELEASE

NVM Express Workgroup Holds First Plugfest

Milestone in Process to Deliver Standards-based Interoperability for PCI Express

Solid-State Drives

WAKEFIELD, Mass., May 29, 2013 – The <a href="NVM Express Workgroup">NVM Express P(Cle)</a> bus, held its first Plugfest at the University of New Hampshire InterOperability Lab in Durham, N.H., May 13-16, 2013. This event provided an opportunity for participants to measure their products' compliance with the NVM Express (NVMe) specification and to test interoperability with other NVMe products.

The NVMe specification defines an optimized register interface, command set and feature set for PCIe-based Solid-State Drives (SSDs). NVM refers to non-volatile memory, as used in SSDs. The goal of NVMe is to unlock the potential of PCIe SSDs now and in the future, and to standardize the PCIe SSD interface. Participating in the Plugfest were Agilent Technologies, Dell Inc., Fastor Systems, Inc., HoST, a Western Digital company, Integrated Device Technology, Inc., Intel Corporation, Samsung Electronics Co., Ltd., SanDisk Corporation., sTec, Inc., Teledvne LeCrov, and Western Digital Corporation.

NVMe products targeting Datacenter shipping this year

**IDF**13

44

# **NVME DELIVERS IN PERFORMANCE**

### **NVM Express\* (NVMe) Delivers Best in Class IOPs**

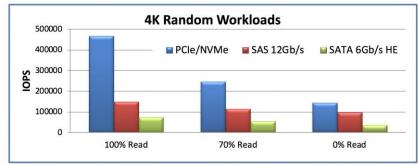

• 100% random reads: NVMe has >3X better IOPs than SAS 12Gbps

70% random reads: NVMe has >2X better IOPs than SAS 12Gbps

• 100% random writes: NVMe has ~ 1.5X better IOPs than SAS 12Gbps

Note: PCI Express' (PCIe\*) NVM Express' (NVMe) Measurements made on intel\* Core\* 17-37705 system @ 3.1GHz and 4GB Mem running Windows' Server 2012 Standard O/S, Intel PCIe/NVMe SSDs, data collected by Olmeter' tool. PCIe/NVMe SSDs is under development. SAS Measurements from HGST Ultrastar' SSDs00/H100M (SAS) Solid State Drive Specification. SATA Measurements from Intel SG Islandard O/S, Intel PCIe/NVMe SSDs, data collected by Product Specification. Software and workloads used in performance tests may have been optimized for performance only on Intel Intel Interoprocessors. Performance tests, such as SYSmark, and MobiledHeaft, are measured using specific computer systems, component sets such as SYSmark, and MobiledHeaft, are measured using specific computer systems, component sets such as SYSmark, and MobiledHeaft, are measured using specific computer systems, component sets such as SYSmark, and MobiledHeaft, are measured using specific computer systems, component sets such as SYSmark, and MobiledHeaft, are measured using specific computer systems, component sets such as SYSmark, and MobiledHeaft, are measured using specific computer systems, component sets such as SYSmark, and MobiledHeaft, are measured using specific computer systems, component sets such as SYSmark, and MobiledHeaft, are measured using specific computer systems, component sets such as SYSmark, and MobiledHeaft, are such as SYSmark, and MobiledHeaft sets as SYSmark, and MobiledHeaft sets are such as SYSmark, and MobiledHeaft sets are such

IDF14

### **And Best in Class Sequential Performance**

- NVM Express\* (NVMe) delivers > 2.5GB/s of read and ~ 2 GB/s of write performance

- 100% reads: NVMe has >2X better performance than SAS 12Gbps

- 100% writes: NVMe has >2.5X better performance than SAS 12Gbps

Note: PCI Express (PCIe\*)/NVMe Measurements made on Intel® Core® 17-37705 system @ 3.1GHz and 4GB Mem running Windows' Server 2012 Standard O/S, Intel PCIe/NVMe SSDs, data collected by IOmeter' tool. PCIe/NVMe SSD is under development. SAS Measurements from Intel Solid State Drive SSD Solid State Drive Specification. SATA Measurements from Intel Solid State Drive SP Product Specification SATA Measurements from Intel Solid State Drive Dr 2770 Series Product Specification Solid State Drive Specification Solid State Drive Drive State Drive Specification Solid State Drive Specification State Drive State D

IDF14

# **EFFICIENTLY AND WITH LOW LATENCY**

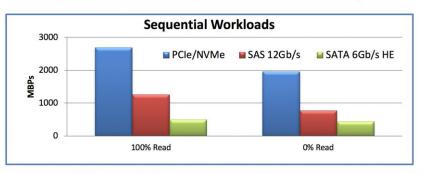

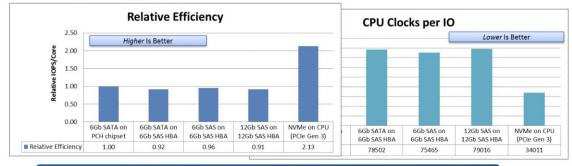

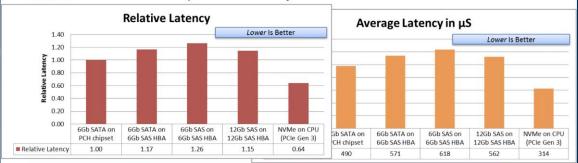

### The Efficiency of NVM Express\* (NVMe)

- CPU cycles in a Data Center are precious

- · And, each CPU cycle required for an IO adds latency

- NVM Express\* (NVMe) takes less than half the CPU cycles per IO as SAS

### With equivalent CPU cycles, NVMe delivers over 2X the IOPs of SAS!

Software and workloads used in performance tests may have been optimized for performance roll on the microprocessors. Performance tests, such as 5'S'pama's and MobileMark', are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating you 17 contemplated purchases, including the performance of that product when combined with other products. For detailed configuration information, refer to "Setup for Efficiency and Latency Analysis" foil in Backup.

### The Latency of NVM Express\* (NVMe)

- The efficiency of NVM Express\* (NVMe) directly results in leadership latency

- When doubling from 6Gb to 12Gb, SAS only reduces latency by  $\sim$  60  $\mu$ S

- NVMe is more than 200 µs lower latency than 12 Gb SAS

### NVMe delivers the lowest latency of any standard storage interface.

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark' and MobileMark', are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating you contemplated purchases, including the performance of that products when combined with other products. For detailed configuration information, refer to "Setup for Efficiency and Latency Analysis" foil in Sackup.

IDF14

# WITH BETTER QUALITY OF SERVICE

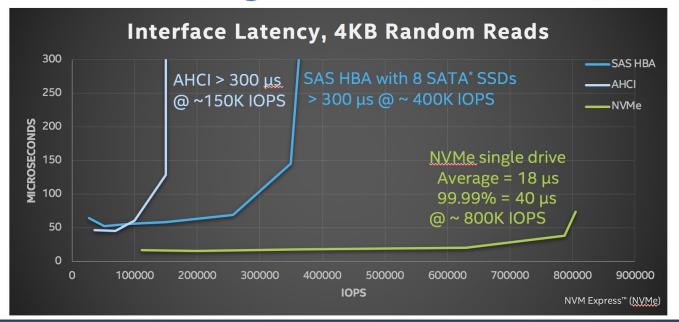

### **NVMe™** Delivers Higher IOPs and Better QoS

NVMe<sup>™</sup> delivers 18 µs average and 40 µs 99.99% interface latency.

Other interfaces have outliers in 100s of µs as interface reaches saturation.

Results measured by Intel based on the following configurations. Intel Server Board S2600WTT with 28 E5-2695 CPUs, 2 sockets, 2.3 GHz clock speed per CPU, Ubuntu\* 14.04.1 LTS (GNU/Linux\* 3.16.0-rc7tickles x86\_64), idle=poll kernel settings, SAS HBA is LSI SAS9207-4i4e with controller LSI SAS 2308. SATA SSDs are Intel\* SSD DC 3500 at 800 GB. NVMe SSD is Intel SSD P3700 at 1.6 TB. Workload details are Workload: 4K Random Reads using FIO – 4 + threads. Drives tested empty to test interface only (no NVM access.)

# AND ANALYSTS NOTICE

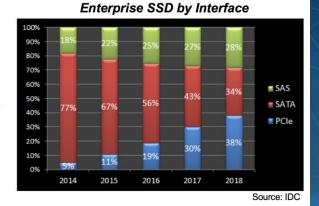

### PCI Express\* (PCIe\*) SSDs Projected to Lead in Data Center

- PCI Express\* (PCIe\*) projected as leading SSD interface in DC by 2018

- PCIe leads in performance

- PCIe bandwidth is significantly higher than SAS or SATA

- NVM Express\* (NVMe) has lower latency than SAS or SATA

- Industry standards for PCIe in place

- NVMe is the software interface

- SFF-8639 defines a 2.5" form factor

PCIe SSDs lead the way by embracing industry standards.

IDF14

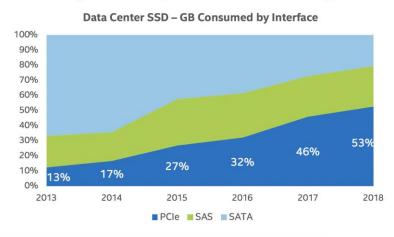

### **Data Center Interface Dynamics, One Level Deeper**

- PCI Express\* (<u>PCle</u>\*) is projected to lead even sooner by capacity

- More NVM is shipped in each <u>PCle</u> SSD than with other interfaces

PCIe projected to lead in NVM shipped to Data Center in 2016.

Source: Intel Market Model and multiple industry analysts

IDF14

# **NVME CONTINUES TO ADD CAPABILITIES**

# AND HEADS TO NEW FRONTIERS ....

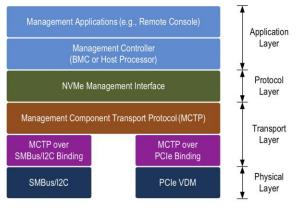

### **NVM Express\* (NVMe) Management Interface**

- · Defines out-of-band management that is independent of the physical transport and protocol

- Maps the management interface to one or more out-of-band physical interfaces (e.g., I2C, PCI Express\*)

- Specifies a management command set for NVM Express\* (NVMe) devices

The management interface is targeted for completion end of year.

IDF14

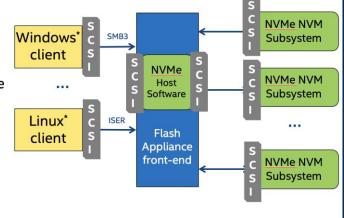

### **NVM Express\* (NVMe) in Fabric Environments**

- A primary use case for NVM Express\* (NVMe) is in a Flash appliance

- Hundreds or more SSDs may be attached - too many for PCI Express\* based attach

- · Concern: Remote SSD attach over a fabric uses SCSI based protocols today - requiring protocol translation

Desire best performance and latency from SSD investment over fabrics like Ethernet, InfiniBand™, Fibre Channel, and Intel® Omni Scale Fabric.

# DRIVING INNOVATION IN **CLOUD**

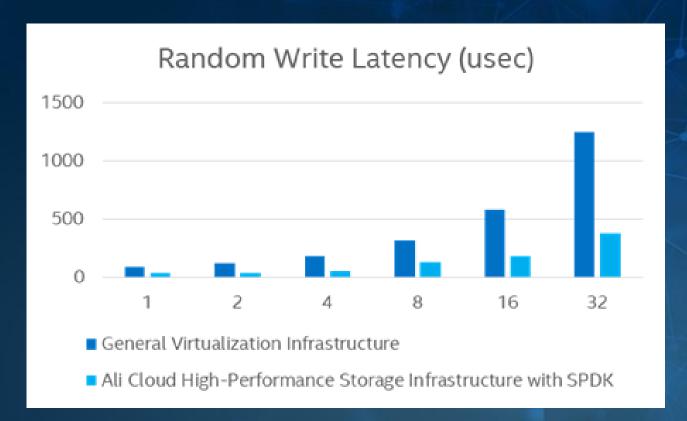

### **Broad Adoption of NVM Express\*** • NVM Express (NVMe\*) delivers speed Latency (uS) required by Cloud Service Providers 10,000 200 NVMe is ready for Intel® Optane™ SSDs 175 150 Local SSD performance depends heavily on which interface you select. Local SSDs are available 125 through both SCSI Z and NVMe Z interfaces. If you choose to use NVMe, you must use a special 100 NVMe-enabled image to achieve the best performance. For more information, see Choosing a disk 75 Google Cloud Platform 50 25 SSD NAND +SAS/SATA +NVMe Source: Storage Technologies Group, Intel. Comparisons between ■ Drive Latency ■ Controller Latency ■ Software Latency memory technologies based on in-market product specifications and internal Intel specifications.

# **EVEN MORE CAPABILITIES ... NVME REVISION 1.3**

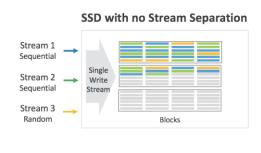

# STREAMS, VIRTUALIZATION, AND MORE

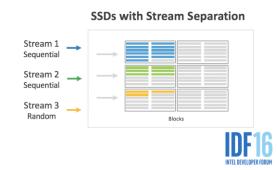

### **Directives: Streams**

- Allows a host to physically segregate ~ 10 20 streams of data

- If host manages data well, reduces write amplification

- E.g., stream 3 no longer interferes with stream 1 and stream 2

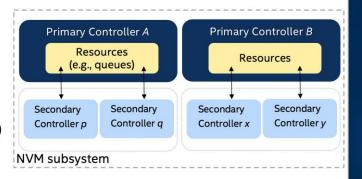

### **Direct Assignment Support in NVMe\***

- There is a hierarchy of primary and secondary controllers

- The near term approach maps onto PCIe\* SR-IOV

- primary = physical function (PF)

- secondary = virtual function (VF)

- Abstraction allows future mechanisms beyond SR-IOV

Industry's first definition of standard SR-IOV driver across vendors.

IDF16

INTEL DEVELOPER FORUM

25

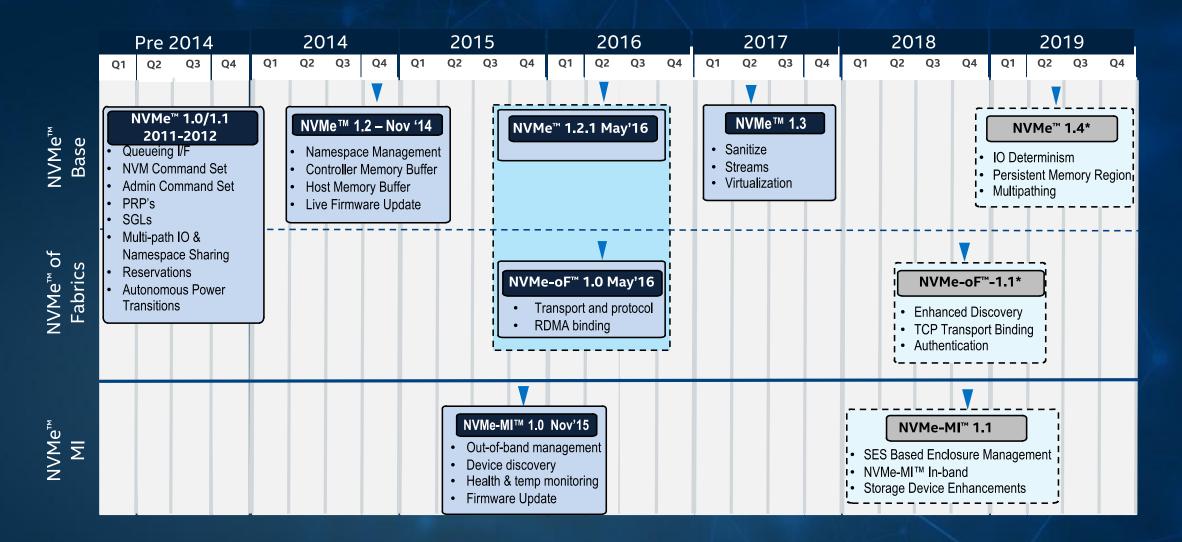

# LATEST NVME ROADMAP

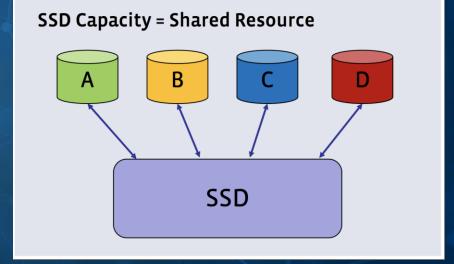

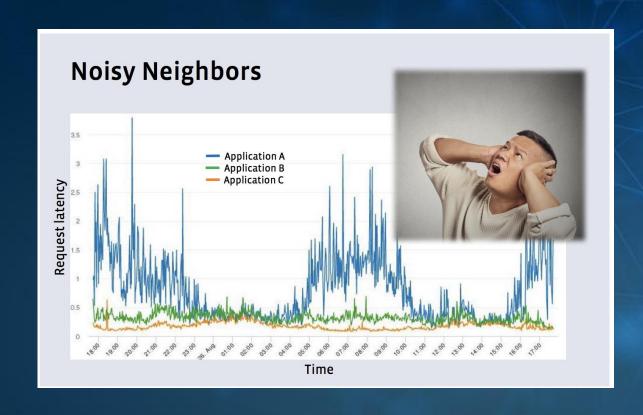

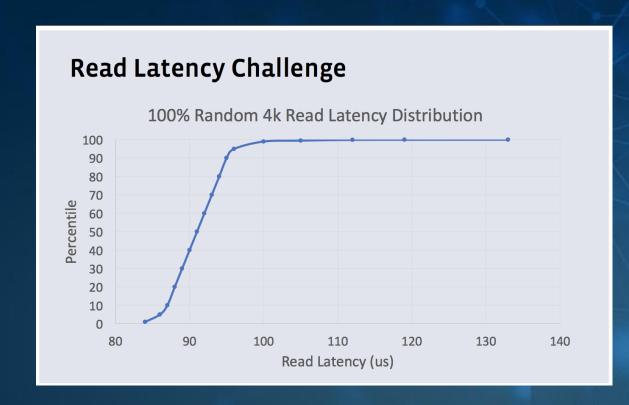

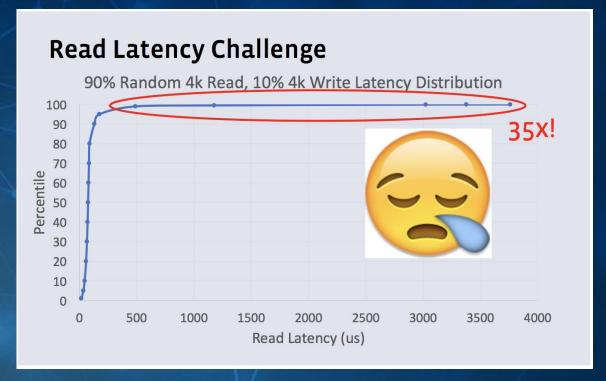

# TODAY'S CHALLENGE QUALITY OF SERVICE AT SCALE

# TODAY'S CHALLENGE QUALITY OF SERVICE AT SCALE

# Latency vs. Bandwidth Image source: pixabay.com

# TODAY'S CHALLENGE QUALITY OF SERVICE AT SCALE

# CALL TO ACTION SOLVE QOS AT SCALE

There are many approaches to solve quality of service at scale.

Collectively, embrace ONE path forward and SCALE the solution.

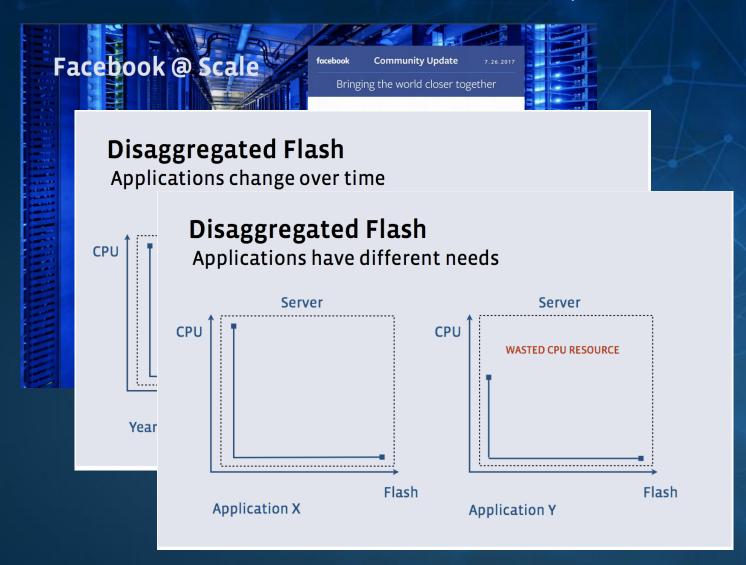

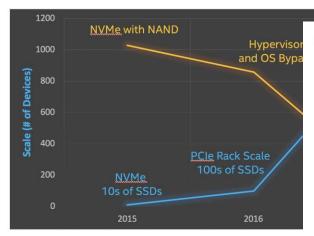

# SCALING THE NUMBER OF SSDS ENTER FABRICS

# WHY NVME OVER FABRICS

### The EMC Perspective

Next generation high-speed big-data apps require a new architecture

The Need to Extend NVM Express™ Over Fabrics

- PCI Express<sup>®</sup> ideal for in-server and in-rack, but difficult to scale beyond 100's of nodes:

- Address routing rather than endpoint routing

- Want to converge storage + networking at scale

- Want to leverage standard switch infrastructure

- Existing Fabric interface (e.g., iSER / SRP) ecosystem is not well suited for this:

- Inconsistent adoption across OS/VMs

- Protocol is overly complex, adding latency

- Issues even worse when we move to NG-NVM

Delivering < 20 µs across Fabric requires n

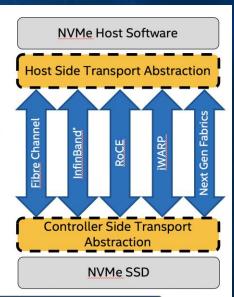

### **NVM Over Fabrics Overview**

- The back-end of many deployments is PCIe Express<sup>®</sup> based NVM Express<sup>™</sup> (NVMe) SSDs

- With 10-100Gb reliable RDMA fabric and NVMe SSDs, the remaining issue is the software necessary to execute the protocol

- Use NVMe end-to-end to get the simplicity, efficiency, and low latency

- Simple protocol => Simple host and SSD software

- No translation to/from another protocol like SCSI

Standard abstraction layer enables NVMe across range of Fabrics

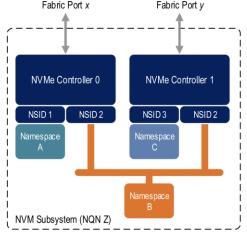

# ARCHITECTURE OF FABRICS

### **Solid Architecture Foundation to Leverage**

- NVM Express<sup>™</sup> (NVMe) revision 1.2 defines solid architecture to leverage

- NVM Subsystem Architecture

- Multiple NVMe Controllers and fabric ports

- Multi-path I/O and multi-host support

- Namespace Architecture

- Multiple (shareable) namespaces

- Namespace management & reservations

- Multiple I/O Queue host interface

- Simple command set, optimized for NVM

- SGL based buffer descriptors

27

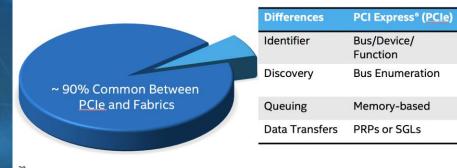

### **Commonality Between PCI Express® and Fabrics**

- The vast majority of NVM Express<sup>™</sup> (NVMe) is leveraged as-is for Fabrics

- NVM Subsystem, Namespaces, Commands, Registers/Properties, Power States, Asynchronous Events, Reservations, etc.

- Primary differences reside in enumeration and queuing mechanism

Fabrics

(NQN)

Discovery and Connect commands

Message-based

SGLs only, added Key

**NVMe Qualified Name**

# **NVME OVER FABRICS 1.0 DELIVERED IN 2016**

### **Solutions Coming Soon**

- Revision 1.0 published on June 5

- Linux\* host and target driver published simultaneously

- More than 20 companies participated

- Proof of concepts shown by ~10 companies with products imminent

- Showing << 10 μs latency added

Get ready for NVM Express\* over Fabrics products appearing later this year!

20

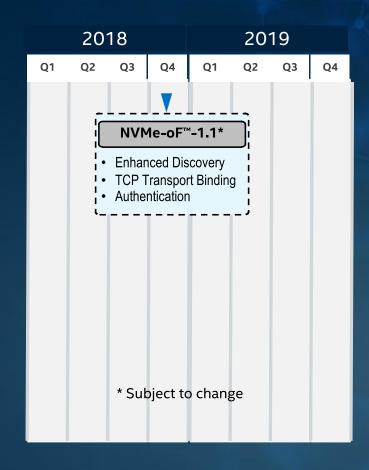

# INTRODUCING TCP AS A TRANSPORT

Alternative to iSCSI to realize full benefits of NVMe end to end.

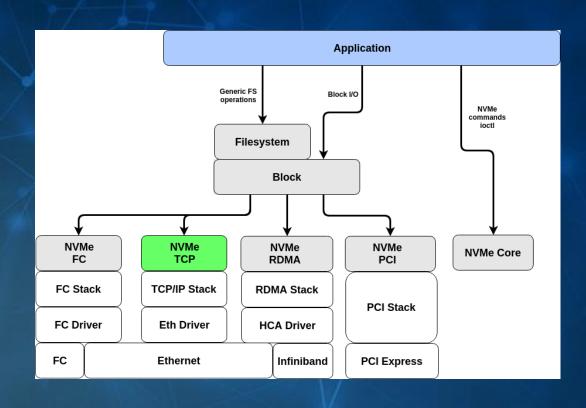

## **SOFTWARE PLAYS KEY ROLE**

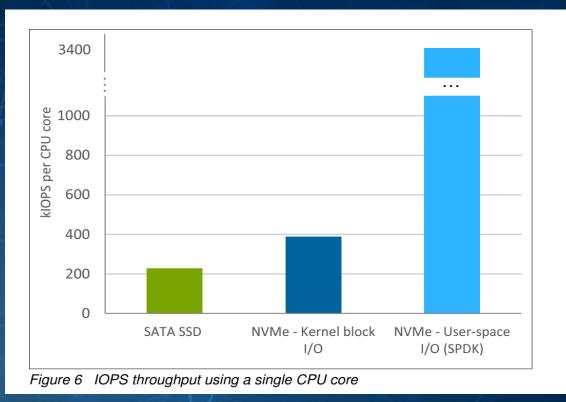

SPDK provided a boost with more IOPS/Core and less overhead.

# CONNECTORS, FORM FACTORS, OH MY...

# ENABLING 2.5" PCIE\* SSD, NOW KNOWN AS U.2

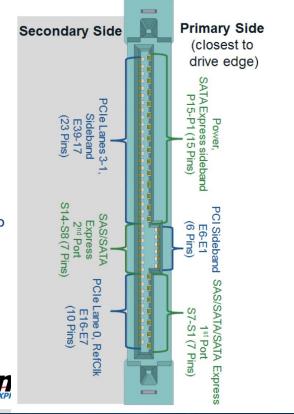

## **SSD Form Factor Working Group** *Driving Enterprise SSD Infrastructure*

Benefit from current 2.5" HDD form factor

Expand power envelope

Support Multiple Protocols

PCI Express\* 3.0, SAS 3.0, SATA 3.0

Management Bus

Dual port (PCIe)

Multi-lane capability (PCIe/SAS)

SAS & SATA Backward Compatibility

Hot-Plug Connector Identify desired drive behavior

Define required system behavior

### **Enterprise Connector Status**

- The SSD Form Factor Workgroup is focused solely on Enterprise SSD infrastructure

- Five Promoters direct effort: Dell\*, EMC\*, Fujitsu\*, Intel, and IBM\*

- 45 members contribute to the definition

- 2.5" Form Factor specification released

- Rev 0.85 released to Workgroup members on 9/6

- Previous release (0.72) released to Workgroup members on 2/11

- Drive Connector Pin-out specification released

- Revision 1.0 in March '11 and revision 1.1 in May '11

- Submitted to SFF to actively drive industry alignment for "one connector" for PCI Express\* and SAS, used to create SFF-8639

Get involved - visit www.ssdformfactor.org

23

# **U.2 TAKES SHAPE**

# SFF-8639 Brings Full Storage Capabilities to Enterprise

- SFF-8639 brings a 2.5" pluggable form factor to the Enterprise

- For Enterprise PCle SSDs, this includes support for a typical server and storage configuration

- Server: Single x4 PCle SSD

- Storage: High availability dual ported solution

Flash Memory Summit 2013 Santa Clara, CA

### Typical High Availability Storage configuration

**NVM**

27

# SFF-8639 Flexibility

- SFF-8639 supports:

- Enterprise PCIe x4 SSDs

- Existing SAS drive (dual port)

- Existing SATA drives

- As ecosystem develops:

- Client 2.5" PCle (often referred to as SATA Express)

- x4 SAS

- Supports flexible backplanes

- Enterprise x4 PCle SSDs

- SAS/SATA HDDs

Flash Memory Summit 2013 Santa Clara, CA

# **INVENTING M.2**

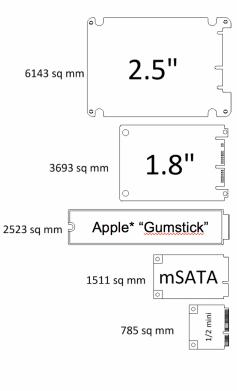

### **Client Form Factors**

- The outline of each client SSD used today is shown to the right

- 2.5" and 1.8" are cased form factors, drop-in HDD replacements

- SSD vendors are being pushed for "one off" custom form factors leading to increased cost

- e.g. gumstick design

- A standard optimized caseless SSD form factor is needed

### **An Optimized Caseless Form Factor**

- Attributes to strive for in a new standardized caseless SSD FF:

- Scalable from small to large capacity points

- Support SATA Gen3 and two lanes of PCI Express\* Gen3

- Optimize for Z height (e.g. board edge connector, reduce PCB thickness)

- Mounting strategy will limit board area and reduce fasteners

- Optimize board size based on BGA NAND package & ensure efficient tiling

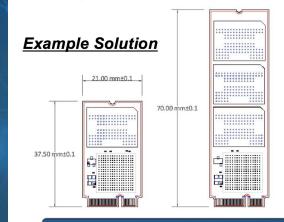

### mSATA vs Example

Watch for new standard caseless form factor effort

20

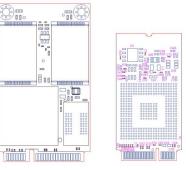

# M.2 EMERGES IN CLIENT

### M.2 Emerging as **Primary Client Form Factor**

- In client, as SSDs move first to PCle, OEMs are using the optimized M.2 form factor

- As native OS support of NVMe becomes pervasive, OEMs will move from AHCI to NVMe to take full advantage of PCIe

Flash Memory Summit 2013 Santa Clara, CA

- 4th gen Intel<sup>®</sup> Core<sup>™</sup> i7 processor available · Windows 8 Pro available

- . Full HD TRILUMINOS IPS touchscreen (1920 x 1080)

- . Super fast 512GB PCIe SSD available · Ultra-light at just 2.34 lbs.

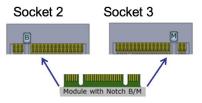

### M.2 Provides OEM Choice: Max Performance or Flexibility

- Three families of modules:

- Socket 1: Wi-Fi/Connectivity only

- Socket 2: WWAN, Storage (SATA\*, PCle\* x1, PCle\* x2), other

- Socket 3: Storage only (SATA\*, PCle\* x1, PCle\* x2, PCle\* x4)

- OEMs choose the socket to include

- Socket 2: Most flexibility

- Socket 3: Highest performance

With M.2, client OEMs can choose maximum performance with 4 lanes, or they can choose flexibility with SATA and WWAN options.

\*Other names and brands may be claimed as the property of others

# BUT ... M.2 AND U.2 KEEP US IN THE "LEGACY BOX"

August 2018

# The Dilemma of Defining The System of Tomorrow – Today

- Typical design point is 2 socket, 1U server

- Configurability is Critical

- Needed today does not mean needed tomorrow

- More stranded IOs = Opportunity lost, wasted \$\$\$

- Ideal scenario: All precious IOs are utilized

- New technologies (e.g., FPGAs) increase the challenge

Santa Clara, CA

### Challenges to Address

### **Need More NVM Sites**

less packages/SSD = more dies/package = lower yield/package

Santa Clara, CA August 2018

### Support SSDs and MORE

Legacy connectors have been SSD only.

### Optimize for NVM

Legacy form factors in Enterprise and Datacenter based on HDDs or client SSDs.

### Thermals and TCO Matter

Legacy SSDs not thermally optimized. Airflow to CPU restricted.

# INVEST FOR THE FUTURE WITH EDSFF

### **Enter EDSFF**

Flash Memory Summit

- General purpose scalable connector

- Flexible: Multiple orientations, widths, PCle\* Gen 5+ support

- Supports interoperable specs (EDSFF, OCP Mezz, Gen Z, etc.)

- Break free of legacy to optimize for NVM

- 50-100% increase in media package sites

- Improved thermal efficiency

- 2-3x less airflow needed

- Or support higher power devices

these these amplitudes comproduct assemblem-considered CDONN Intelligence and the CDONN Intelligence a

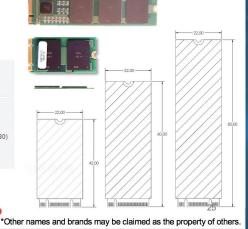

### Scalable Family for Different Usages

### Flash Memory Summit

### E1.L (SFF-TA-1007)

- 318.75 x 38.4 mm

- Supports > 40W

- Up to 48 Standard NAND sites

- Same Protocol: NVMe

- Same Interface: PCle

- Same Connector: SFF-TA-1002

- <u>Same</u> Pinout and Functions (hot plug, serviceable)

- <u>Different</u> Usages, <u>Same</u> Expectations!

Santa Clara, CA August 2018

### E1.S (SFF-TA-1006)

- 111.5 x 31.5 mm

- Supports >12W

- Up to 12 Standard NAND sites

### E3 (SFF-TA-1008)

- (104.9/142.2) x 76mm

- Supports up to 70W

- Up to 48 Standard NAND sites

5

# WE DELIVERED NAND SSD TIER AT SCALE, TOGETHER

# FOCUS OF NVME - ENABLE FUTURE NVM

### **Scalability for Future NVM**

- NVMe\* is defined to scale for future NVM

- Host controller standards live for 10+ years

- Future NVM may have sub microsecond latencies

- 1M IOPS needs highly efficient driver approach

- Benefits from removing OS queues, IO scheduler, and SCSI layer while optimizing for NVMe

- Block layer attach reduces overhead > 50%

- Block layer: 2.8 μs, 9100 cycles

- Traditional: 6.0 µs, 19500 cycles

### **Chatham NVMe Prototype**

Block Layer

Req

Queue

SCSI

Xlat

NVMe

Driver

2.8 µsecs

6.0

Usecs

Linux \*

Storage Stack

User Apps

Kernel

Measurement taken on Intel<sup>®</sup> Core™ i5-2500K 3.3GHz 6MB L3 Cache Quad-Core Desktop Processor using Linux RedHat EL6.0 2.6.32-71 Kernel

# PREPARING THE WAY FOR AN NVM BREAKTHROUGH

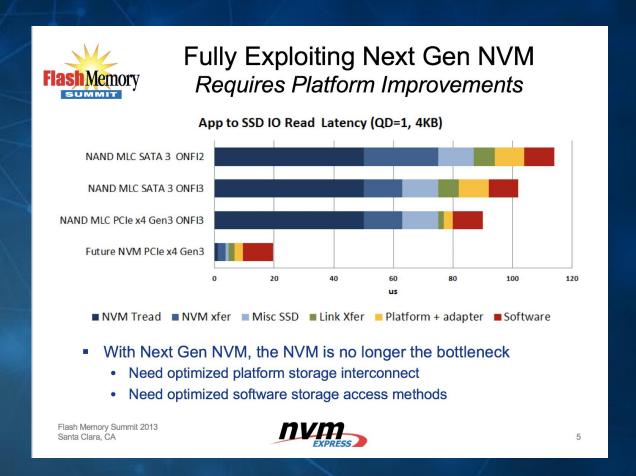

### Flash Memory Summit 2013

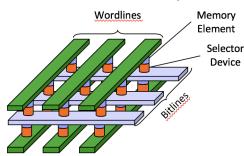

### **Next Generation Scalable NVM**

### Scalable Resistive Memory Element

Cross Point Array in Backend Layers ~4λ2 Cell

### **Resistive RAM NVM Options**

| Family                                  | Defining Switching<br>Characteristics                                                             |

|-----------------------------------------|---------------------------------------------------------------------------------------------------|

| Phase<br>Change<br>Memory               | Energy (heat) converts material between crystalline (conductive) and amorphous (resistive) phases |

| Magnetic<br>Tunnel<br>Junction<br>(MTJ) | Switching of magnetic resistive layer by spin-polarized electrons                                 |

| Electrochemical<br>Cells (ECM)          | Formation / dissolution of<br>"nano-bridge" by <u>electrochemistry</u>                            |

| Binary Oxide<br>Filament<br>Cells       | Reversible filament formation by<br>Oxidation-Reduction                                           |

| Interfacial<br>Switching                | Oxygen vacancy drift diffusion induced barrier modulation                                         |

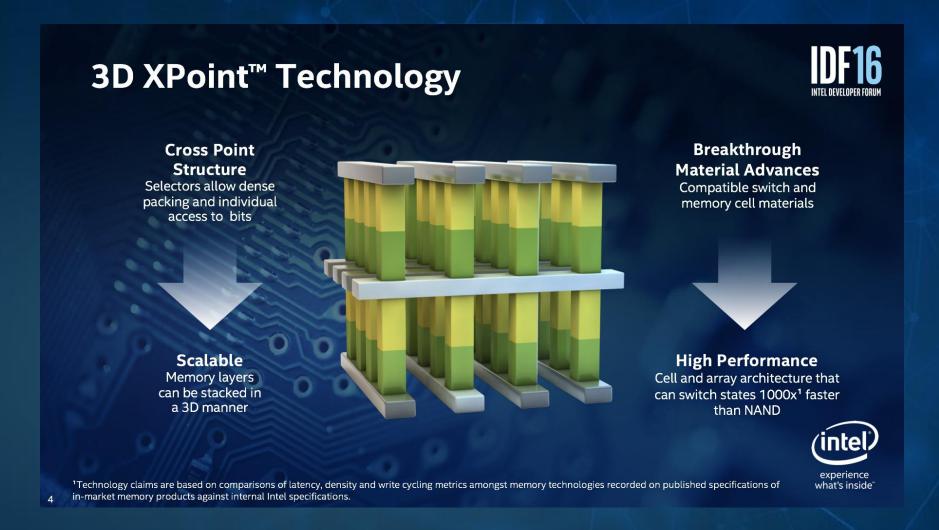

Many candidate next generation NVM technologies.

Offer ~ 1000x speed-up over NAND, closer to DRAM speeds.

Santa Clara, CA

For full SSD benefits, must architect for NVM from ground up.

# THE BREAKTHROUGH

# REIMAGINING THE HIERARCHY

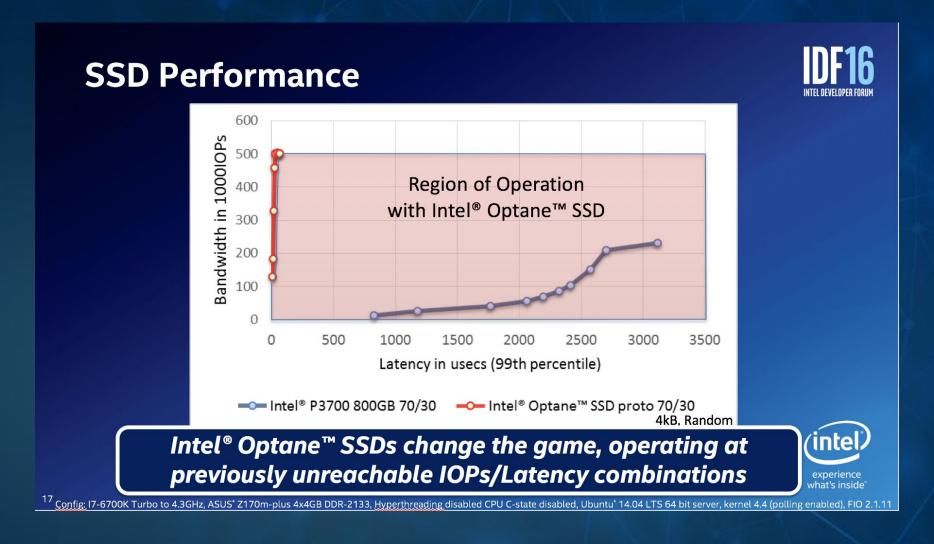

# WITH PREVIOUSLY UNREACHABLE PERFORMANCE

# PROOF POINT: CASSANDRA 4.0\* DATABASE

IOPS performance vs. Comparable Server System with DRAM and NAND SSD

SSD DC P4800X Intel® Optane™ SSD DC P4800X W/ Direct I/O\* Java optimizations

SSD DC P4800X W/ Direct I/O\* Java optimizations

SSD DC P4800X W/ Direct I/O\* Java optimizations

available Intel® Optane™ DC SSDs

with available software tools

# **3** EVOLVE

with next-generation memory technology

1 System configuration: Server model: 2x Intel® Xeon® E5 2699 v4 @ 4. Ghz, Intel system board S2600WFWF, 384GB DDR4 @ 2667Mhz, 4x Intel® Optane DC SSD 375GB; CentOS 7.3.1611 (kernel 4.17.6), Network is 10GbE. Apache Cassandra version 4.0-SNAPSHOT (DirectIO from Intel-based Java DirectIO Development team). Cassandra-stress tool used for benchmarking embedded into the Cassandra version build 4.0. Java heap size 64GB, Java Garbage collector G1GC, Java Version Oracle JDK 10.01 that embeds with Cassandra. Experimental release used for Optane Persistent Memory based system. Baseline nvme NAND Intel Drives – Intel SSD DC P4510. Baseline consists of Operating System OS page cache (not DirectIO) and best methods per Datastax and lead Companies of the Apache Cassandra Open Source version Project Management Committee. Performance results are based on testing as of July 2018 and may not reflect all publicly available security updates. See configuration disclosure for details. No product can be absolutely secure.

\* Other names and brands may be claimed as the property of others

# THE EMERGING HIERARCHY

# REMEMBER THE EVER INCREASING ZETABYTES

### **Global Digital Data Created (ZB)**

# WE HAVE INVENTED THE FUTURE TOGETHER

LET'S CONTINUE OUR WORK OVER THE NEXT DECADE