Storage Developer Conference September 22-23, 2020

### Update on the JEDEC DDR5 NVRAM Specification

Bill Gervasi Principal Systems Architect bilge@nantero.com

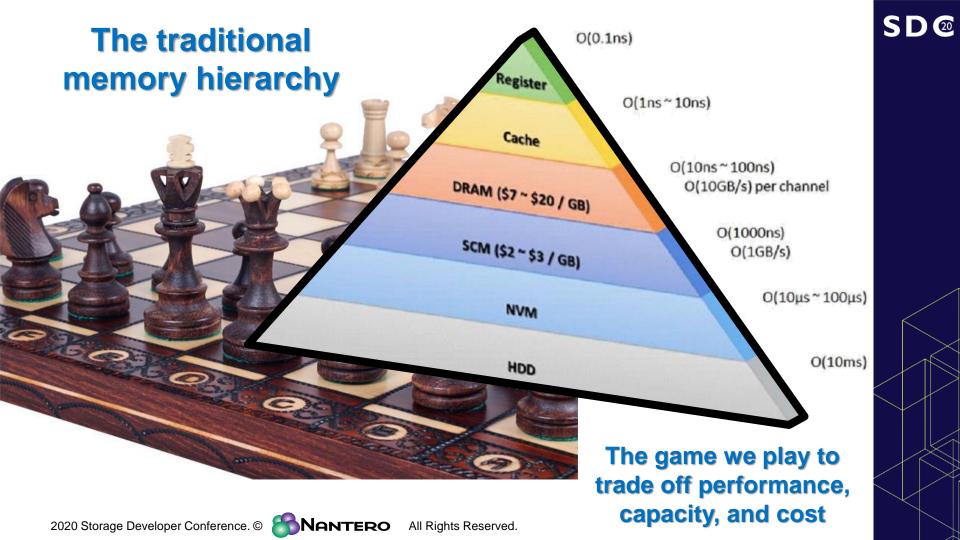

#### How non-volatility **Volatility and** for main memory **NVRAM:** the non-volatility in changes things the memory standard for hierarchy main memory Agenda **Call to Action** Changing system architectures

All Rights Reserved.

**Nantero NRAM**<sup>™</sup>

coming

SD@

SD@

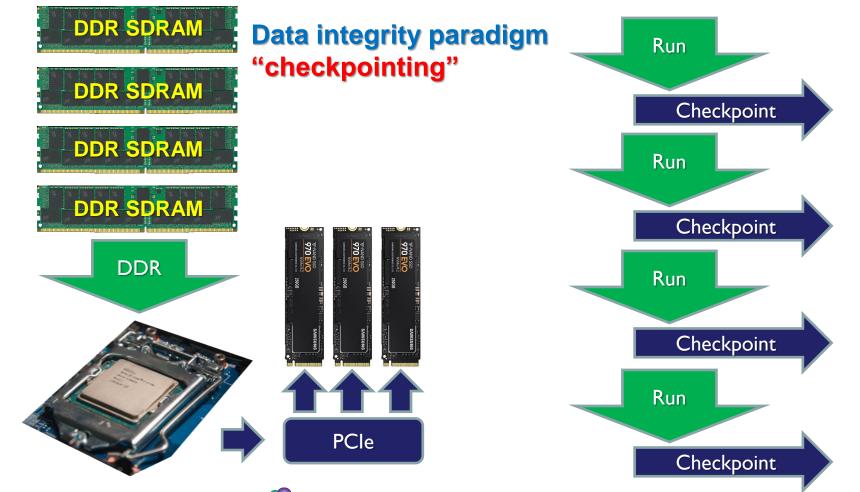

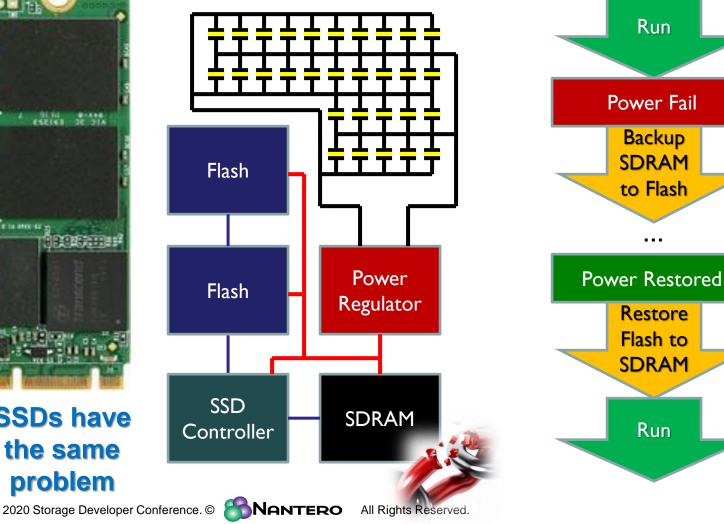

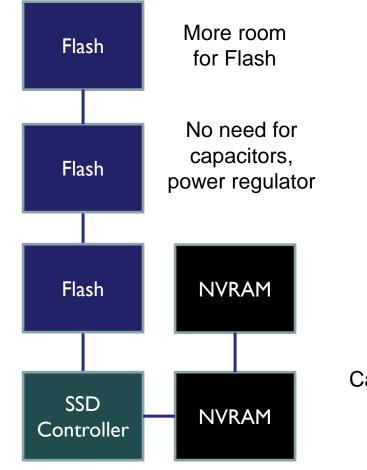

# ...of power failure

# FEAR ...of data loss

All Rights Reserved.

SD @

2020 Storage Developer Conference. ©

SD@

SD@

2020 Storage Developer Conference. ©

All Righ

2020 Storage Developer Conference. ©

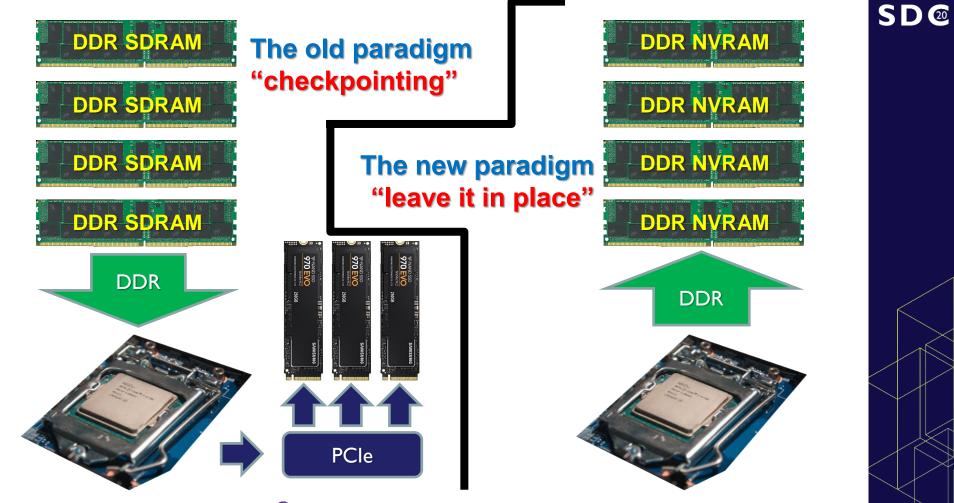

**Obviously not all** storage goes away

> What storage is used for can change

There are data sets that don't fit in memory Data set size is, however, application dependent There are system failures besides power fail The time between checkpoints is vastly different

SD<sub>20</sub>

SD@

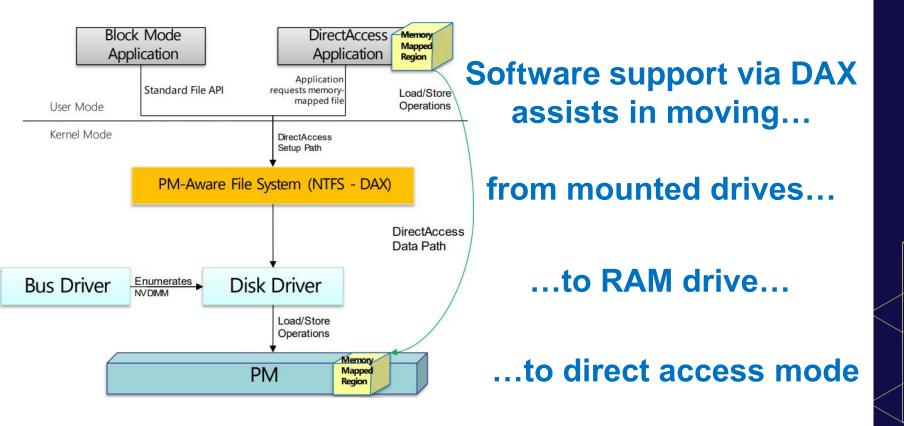

### but software is the tail that wags this dog

2020 Storage Developer Conference. © **Solution** All Rights Reserved.

### **Helping software migrate**

SD<sub>20</sub>

### SD@

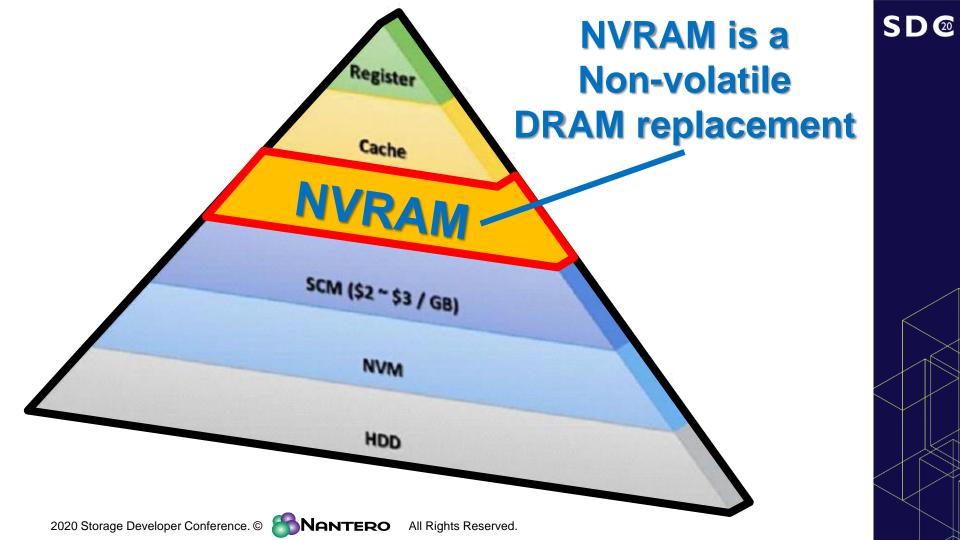

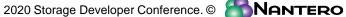

### To Replace DRAM, **NVRAM MUST HAVE**

**Full DRAM speed**

No wear-out

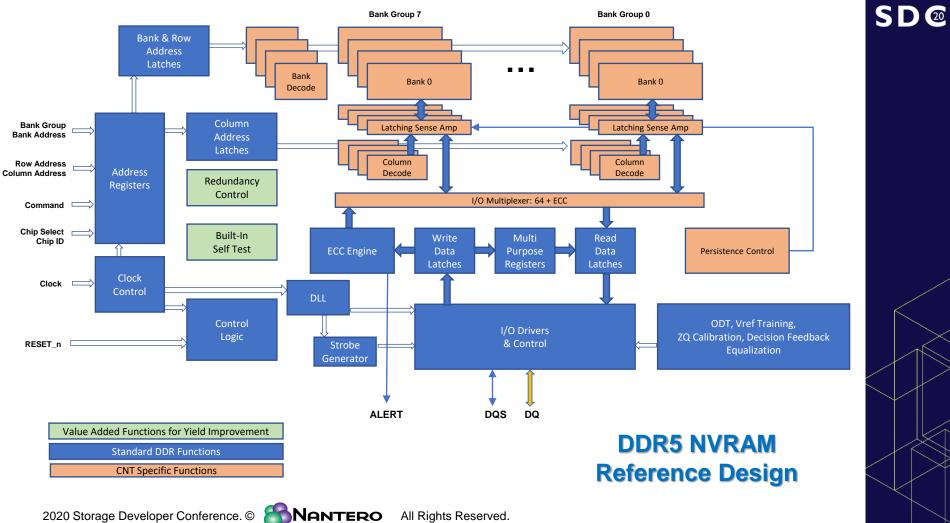

**DRAM capacity or greater**

**DRAM** price

to be the ultimate **Persistent Memory**

SD@

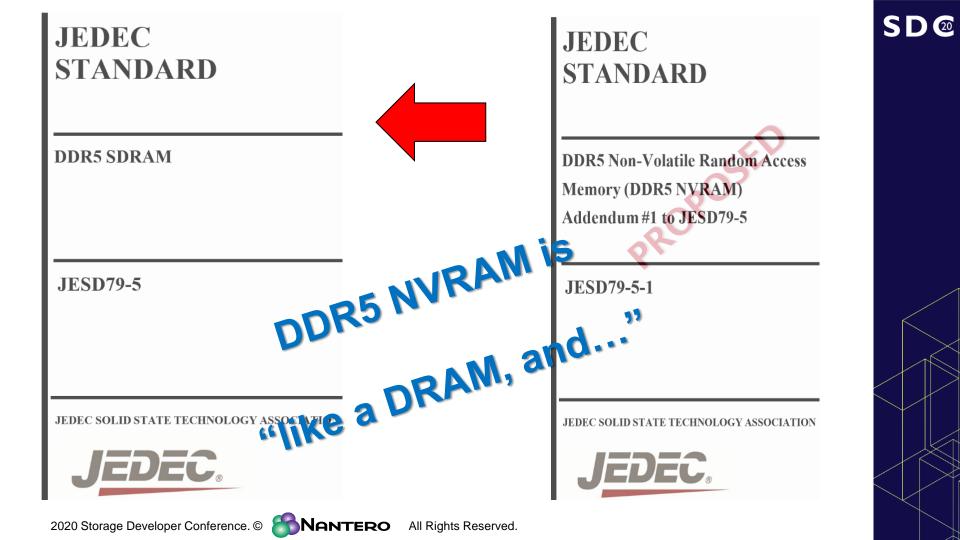

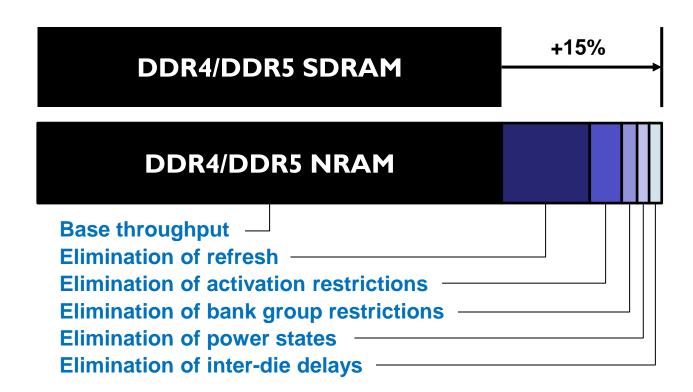

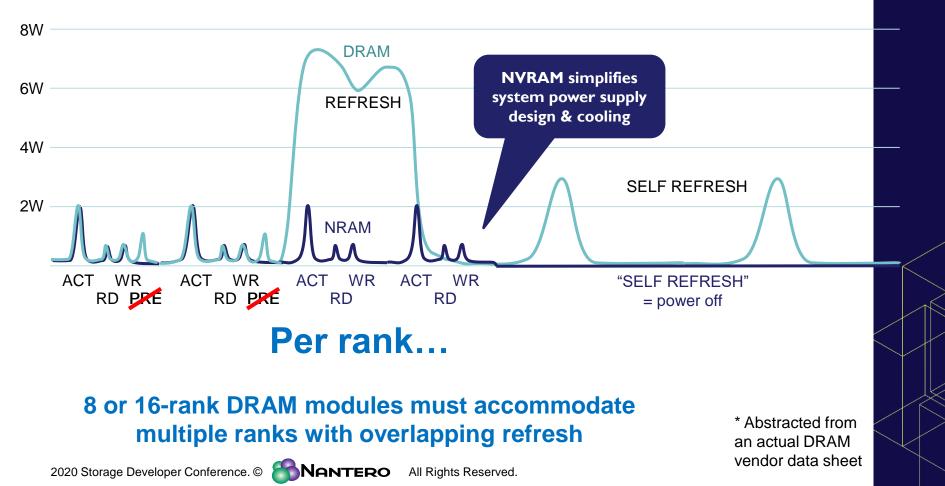

### **Comparing DRAM & NVRAM**

No refresh is required

#### "Self refresh" can be power OFF

#### **Timing compatible**

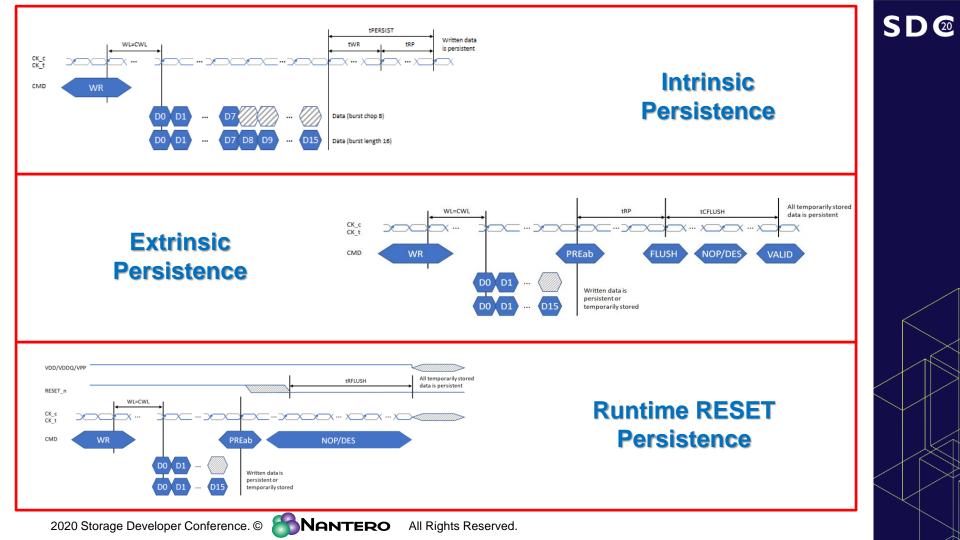

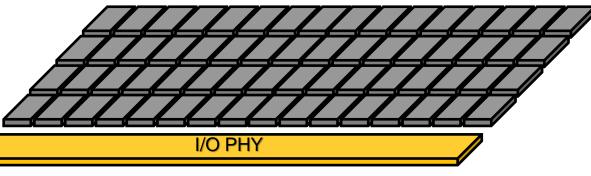

**New: data persistence definitions**

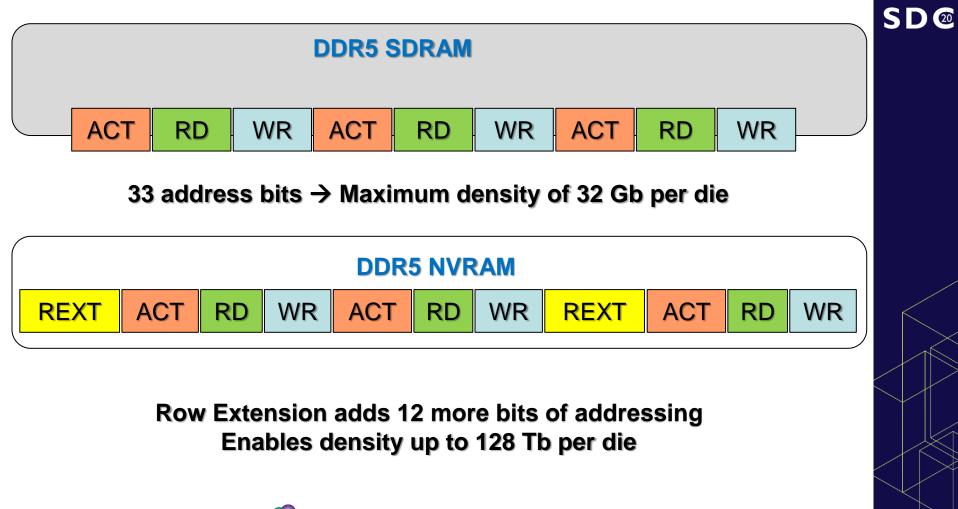

#### Greater per-die capacity

SD@

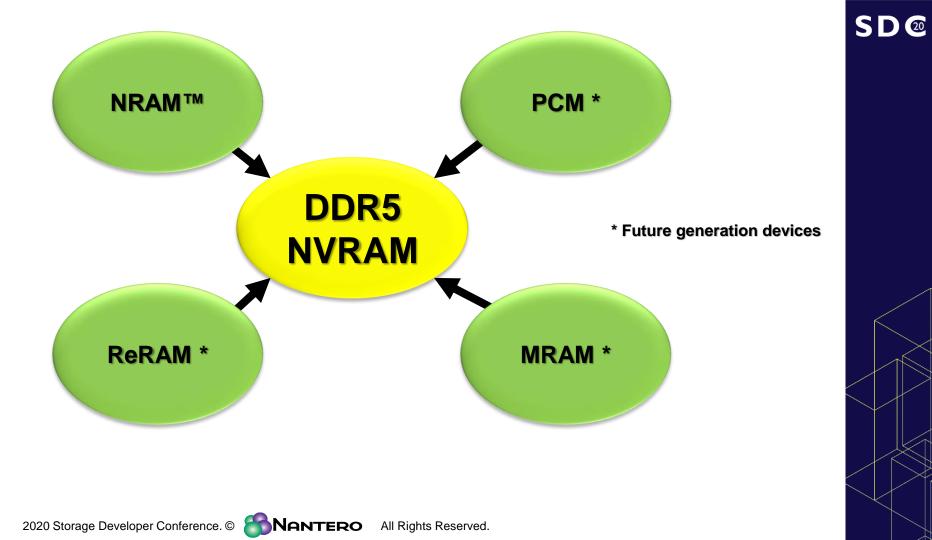

## Differences between media types represented as "Profiles" NRAM PCM MRAM ReRAM

Command needed for "housekeeping"?

Do pages remain open or need to be closed?

Is some kind of flush needed for internal buffering?

#### Organization of pages, banks, bank groups

SD<sub>20</sub>

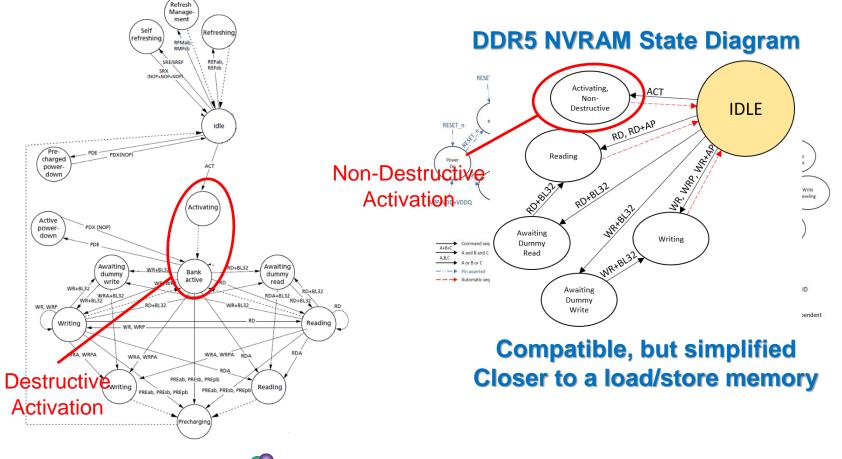

#### **DDR5 SDRAM State Diagram**

2020 Storage Developer Conference. ©

2020 Storage Developer Conference. © **Source New Terror**

2020 Storage Developer Conference. ©

And now, a plug from our sponsor...

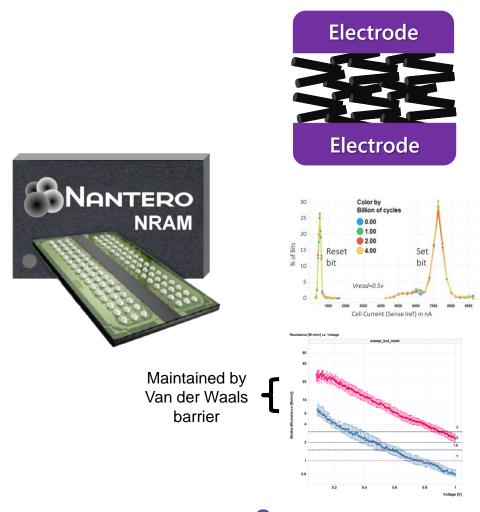

Carbon nanotubes (CNTs) switch freely in a dielectric-free space...

#### ...in 5ns (Write or Read)...

# ...resulting in a permanent cell resistance change

### SD@

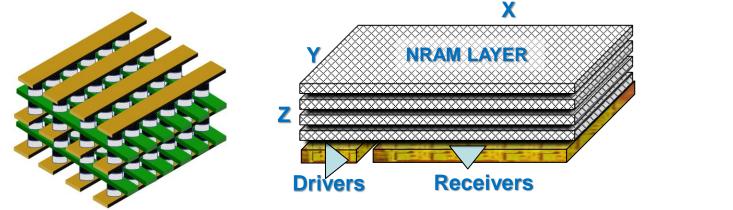

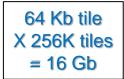

Tune the array size to the size of drivers & receivers **Core-level timing is dominated by word & bit line flight times** Replicate this "tile" as needed for device capacity Add I/O drivers to emulate any PHY needed & meet chip timing

SD@

2020 Storage Developer Conference. ©

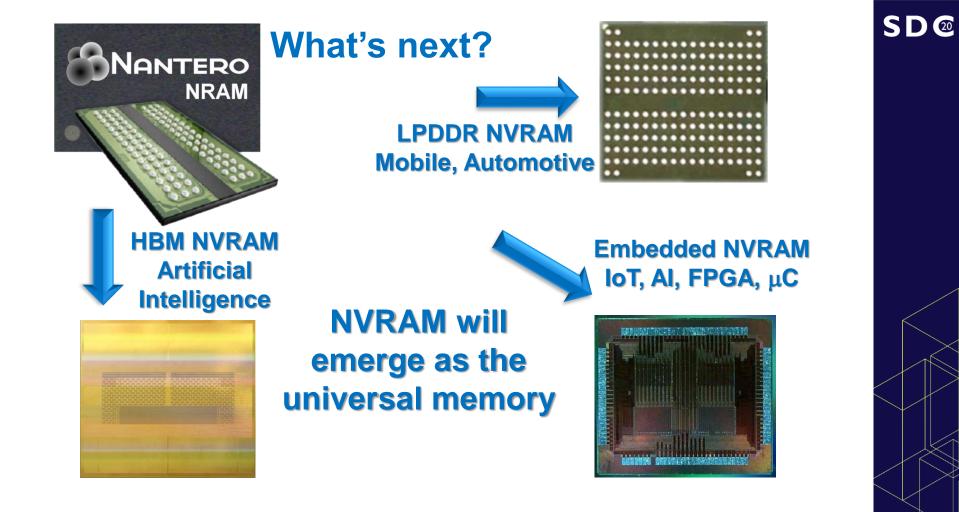

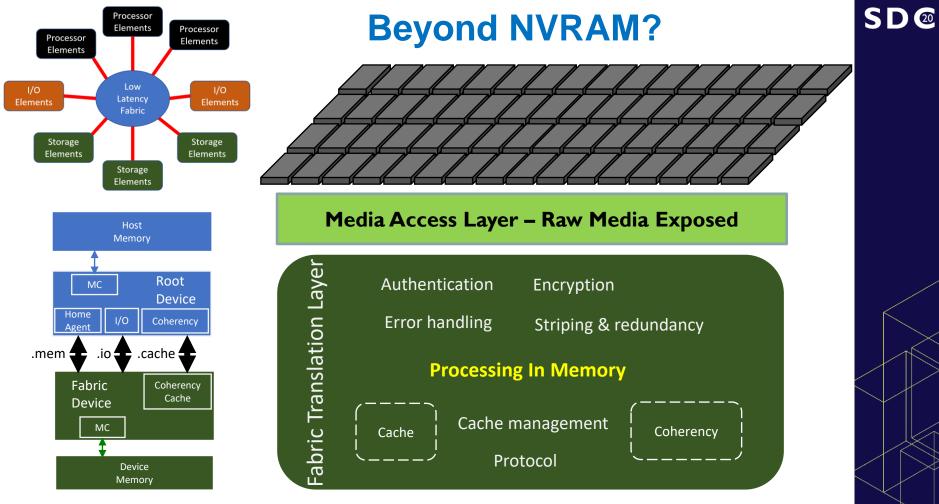

### **NVRAM Memory Class Storage**

SD@

### **Plugs into an RDIMM slot** Appears to the CPU as DRAM Memory controller may optionally be tuned for NVRAM

### 512 Gb per die $\rightarrow$ 16 TB per DIMM

### +15% higher throughput at the same clock frequency

2020 Storage Developer Conference. © **MANTERO** All Rights Reserved.

Bandwidth: larger is better

SD (20

#### 72-bit DDR4 Memory Module Active Power Profile \*

SD<sub>20</sub>

2020 Storage Developer Conference. ©

2020 Storage Developer Conference. ©

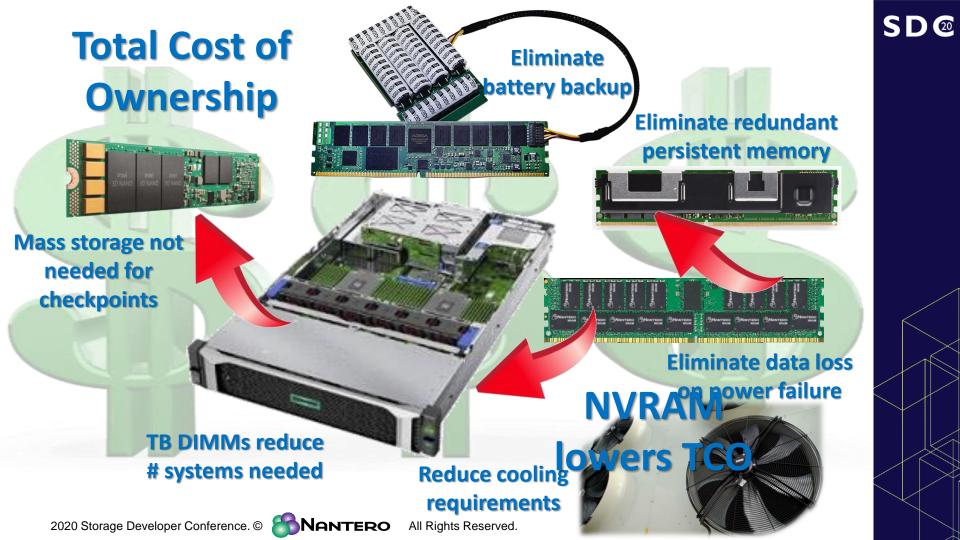

### **Persistent Memory that** replaces DRAM changes everything

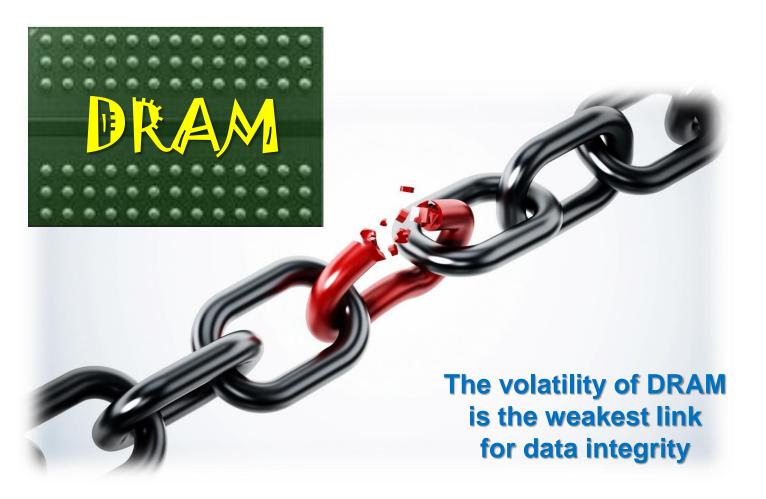

### New models for data integrity will evolve

SD (20

Systems architectures will adapt to exploit leavein-place data

### With DRAM hitting a plateau we all need this in the DDR5 life cycle

2020 Storage Developer Conference. ©

### SD@

### **CALL TO ACTION**

#### Join the JEDEC **Future Memory Task Group** jedec.org

Contact: bilge@Nantero.com

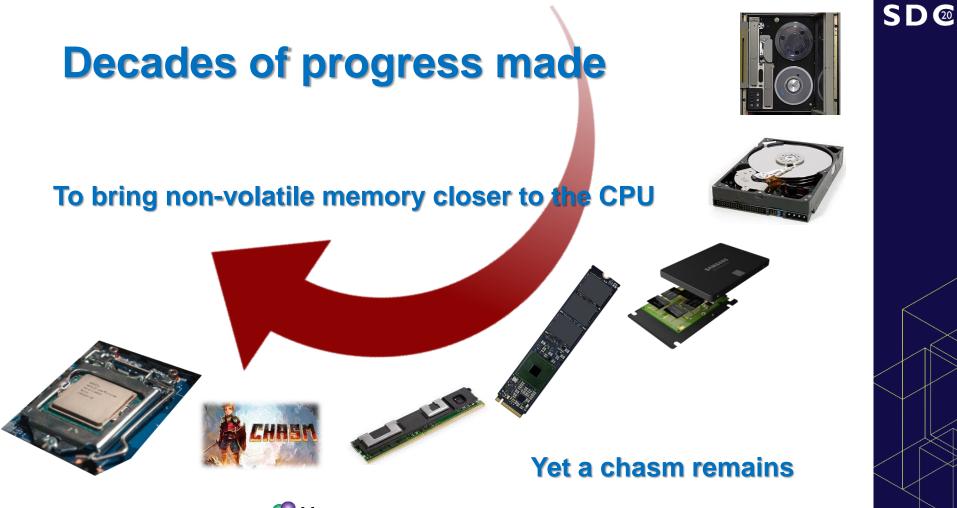

#### Fear of power failure drives architectures

Non-volatility removes that fear factor

NVRAM defines a non-volatile DRAM replacement

SD@

### Summary

Call to Action: get involved!

System architectures are evolving Nantero NRAM™, the best DRAM replacement

2020 Storage Developer Conference. ©

https://www.bridge-to-connect.com

#### BRDG is a non-profit that mentors university students in STEM fields

| October                                                                  |     |     |     |     |     |     |

|--------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|

| Sun                                                                      | Mon | Tue | Wed | Thu | Fri | Sat |

|                                                                          |     |     |     | 1   | 2   | 3   |

| 4                                                                        | 5   | 6   | 7   | 8   | 9   | 10  |

| 11                                                                       | 12  | 13  | 14  | 15  | 16  | 17  |

| 18                                                                       | 19  | 20  | 21  | 22  | 23  | 24  |

| 25                                                                       | 26  | 27  | 28  | 29  | 30  | 31  |

| Phases of the Moon: 1:0 9:0 16:0 23:0 31:0                               |     |     |     |     |     |     |

| Holidays and Observances: 12: Columbus Day (Most regions), 31: Halloween |     |     |     |     |     |     |

Twice a year, BRDG sponsors a technology education event for Southern California educators and technology CEOs 20

"Directions, Applications, and the Future of Artificial Intelligence"

Michael Giering, Research Fellow Raytheon Technologies Research Center

Tuesday, October 20, 2020 4 – 6 PM PDT