## Compute Express Link (CXL) and Persistent Memory: Enabling scalability

#### **Chris Petersen**

## CXL Director Hardware System Technologist, Facebook

# Introducing Compute Express Link (CXL)

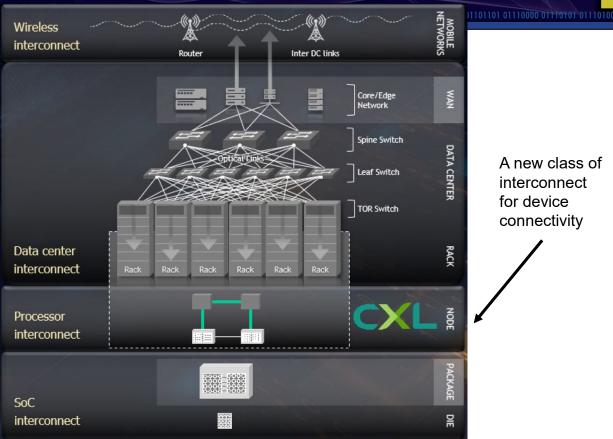

#### Processor Interconnect:

- Open industry standard ٠

- High-bandwidth, low-latency ٠

- Coherent interface ٠

- Leverages PCI Express® ٠

- Targets high-performance • computational workloads

- ✤ Artificial Intelligence

- Machine Learning

- ✤ HPC

- Targets Memory-centric ٠ architectures

#### A new class of interconnect for device connectivity

#### What is CXL?

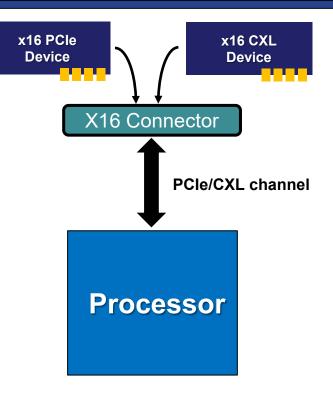

- Alternate protocol that runs across the standard PCIe physical layer

- Uses a flexible CPU port that can autonegotiate to: PCIe or CXL

- First generation CXL aligns to 32 Gbps PCIe 5.0

- CXL usages expected to be key driver for an aggressive timeline to PCIe 6.0

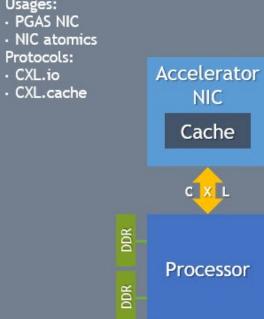

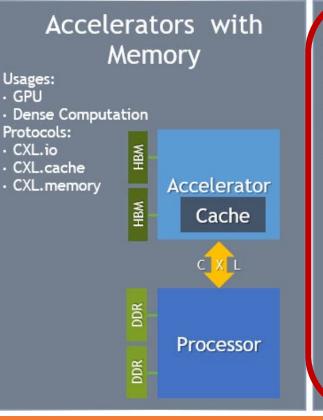

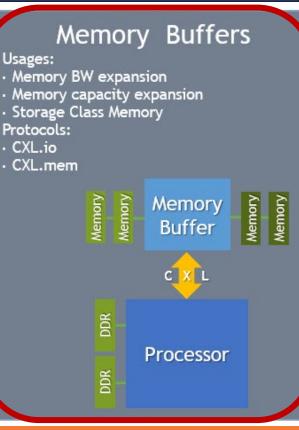

## **Representative CXL Use Cases**

# CXL: A Common Memory Interface

CXL provides a common, standard interface for many types of memory [ CXL CXL CXL **CXL** Memory CXL Memory **CXL** Memory Media independence: could be used Expander Expander Expander to connect DDR3/4/5, LPDDR3/4/5, Media Media Media Persistent memory, etc Controller Controller Controller Enables flexibility for different media <u>2/1/2</u> DN/ characteristics (persistence, latency, <u>2/1/2</u> DN/ DDR3/4/5 ΡM BW, endurance, etc) DRAM DRAM Componen Heterogeneous Memory Attach - DIMMs vs CXL

## & DIMMs are not suitable for Heterogeneous Memory types

#### & CXL solves the problem

- Enables a slow memory tier to be completely isolated from main tier

- Minimal interference between CXL and direct attached DRAM DIMMs

- Enables other memory types whose bandwidth is additive to existing platform memory bandwidth

- E.g. DDR4 and DDR5 can coexist in the same platform

- CXL capacity additive to platform memory capacity

- With inevitable move towards 1 DIMM per DDR channel, CXL becomes a cost-effective path for capacity expansion

# CXL: Addressing System Challenges

- 1. Power density

- DIMM slots tend to be power limited to 15-18W (less in more dense platforms)

- CXL enables:

- Separation of DIMM slots and CXL Memory slots

- ✤ Higher power CXL Memory devices (e.g. 25W+)

- 2. Memory channel count scaling

- Parallel DDR\* interfaces require 200+ pins

- CXL enables:

- Less pins per package = more channels or smaller packages

- Lower mother board PCB layer counts

- 3. Form factor flexibility

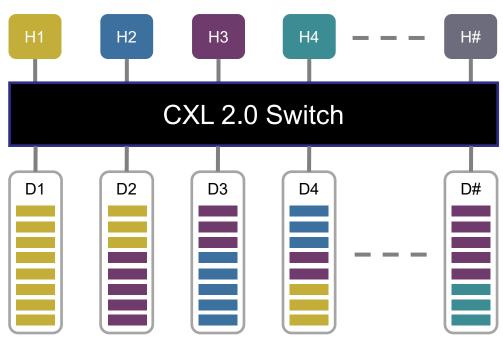

#### What's new in CXL 2.0?

• Pooled memory

Standardized Management Interface

Global Persistent Flush

## **CXL 2.0 Memory Pooling**

#### Memory Pooling with Multiple Logical Devices

Compute Express Link<sup>™</sup> and CXL<sup>™</sup> are trademarks of the Compute Express Link Consortium.

#### Persistent Memory Benefits of CXL 2.0

#### Moves Persistent Memory from Controller to CXL

#### **Enables standardized** Management of the Memory and Interface

#### Supports a Wider Variety of Form Factors

| >       | X    | СРО                                                              | 100                                                          |                   |

|---------|------|------------------------------------------------------------------|--------------------------------------------------------------|-------------------|

| Memory  | DRAM |                                                                  | 101                                                          |                   |

|         |      | CXL                                                              |                                                              | CXL + PM          |

|         |      | Persistent Memory                                                | 10 <sup>2</sup> -10 <sup>3</sup>                             | Fills<br>the Gap! |

| ро<br>О | đ    | Performance SSD                                                  | 104                                                          |                   |

| Storage |      | Capacity SSD                                                     | 105                                                          |                   |

| S       | জ    | HDD                                                              | 10 <sup>6</sup>                                              |                   |

|         |      | Compute Express Link <sup>w</sup> and CXL <sup>w</sup> are trade | nanoseconds<br>marks of the Compute Express Link Consortium. |                   |

#### CXL enables a standardized, scalable persistent memory solution:

- Bandwidth and capacity

- Form factor flexibility

- System design flexibility: Power, Thermal, Complexity, Cost

- Electrical, protocol, and switching interface

- Management interface

- CXL Consortium boasts 130+ member companies to date and still growing

- CXL Consortium Work Groups:

- 5 Technical (Protocol, PHY, Software & Systems, Memory, Compliance) and Marketing

- CXL Board of Directors:

# Call to Action

- CXL ecosystem in the industry continues to grow...

- First anniversary of incorporation second generation specification, working on third generation

- Response to industry needs and challenges

- Fully backwards compatible with CXL 1.1

- Compliance & Interop program

- Call to action

- Join CXL Consortium

- Follow us on <u>Twitter</u> and <u>LinkedIn</u> for more updates!

## Thank You!

# Everything You Need To Know For Success

November 2020