# NVM Programming Model (NPM)

Version 1.1

Abstract: This SNIA document defines recommended behavior for software supporting Non-Volatile Memory (NVM).

This document has been released and approved by the SNIA. The SNIA believes that the ideas, methodologies and technologies described in this document accurately represent the SNIA goals and are appropriate for widespread distribution. Suggestion for revision should be directed to <a href="http://www.snia.org/feedback/">http://www.snia.org/feedback/</a>.

# **SNIA** Technical Position

March 9, 2015

#### USAGE

The SNIA hereby grants permission for individuals to use this document for personal use only, and for corporations and other business entities to use this document for internal use only (including internal copying, distribution, and display) provided that:

- 1. Any text, diagram, chart, table or definition reproduced shall be reproduced in its entirety with no alteration, and,

- 2. Any document, printed or electronic, in which material from this document (or any portion hereof) is reproduced shall acknowledge the SNIA copyright on that material, and shall credit the SNIA for granting permission for its reuse.

Other than as explicitly provided above, you may not make any commercial use of this document, sell any or this entire document, or distribute this document to third parties. All rights not explicitly granted are expressly reserved to SNIA.

Permission to use this document for purposes other than those enumerated above may be requested by e-mailing tcmd@snia.org. Please include the identity of the requesting individual and/or company and a brief description of the purpose, nature, and scope of the requested use.

All code fragments, scripts, data tables, and sample code in this SNIA document are made available under the following license:

BSD 3-Clause Software License

Copyright (c) 2015, the Storage Networking Industry Association.

Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

\* Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

\* Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution.

\* Neither the name of The Storage Networking Industry Association (SNIA) nor the names of its contributors may be used to endorse or promote products derived from this software without specific prior written permission.

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

## DISCLAIMER

The information contained in this publication is subject to change without notice. The SNIA makes no warranty of any kind with regard to this specification, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. The SNIA shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this specification.

Suggestions for revisions should be directed to http://www.snia.org/feedback/.

Copyright © 2015 SNIA. All rights reserved. All other trademarks or registered trademarks are the property of their respective owners.

#### **Revision History**

Changes since version 1:

- The former informative Consistency annex is reworded and moved to two places in the specification body:

- New section 6.10 Aligned operations on fundamental data types

- New section 10.1.1 Applications and PM Consistency in NVM.PM.FILE

- A number of editorial fixes to make spelling, terminology, and spacing more consistent

# Table of Contents

| FO | RE  | WORD                                               | . 9 |

|----|-----|----------------------------------------------------|-----|

| 1  |     | OPE                                                |     |

| 2  |     | FERENCES                                           |     |

| 3  | DE  | FINITIONS, ABBREVIATIONS, AND CONVENTIONS          |     |

| 3  | 5.1 | DEFINITIONS                                        | 12  |

| 3  | .2  | Keywords                                           | 13  |

| 3  | .3  | ABBREVIATIONS                                      | 13  |

| 3  | .4  | CONVENTIONS                                        | 14  |

| 4  | ov  | ERVIEW OF THE NVM PROGRAMMING MODEL (INFORMATIVE)  | 15  |

| 4  | .1  | HOW TO READ AND USE THIS SPECIFICATION             | 15  |

| 4  | .2  | NVM DEVICE MODELS                                  | 15  |

| 4  | .3  | NVM PROGRAMMING MODES                              | 17  |

| 4  | .4  | INTRODUCTION TO ACTIONS, ATTRIBUTES, AND USE CASES | 19  |

| 5  | со  | MPLIANCE TO THE PROGRAMMING MODEL                  | 21  |

| 5  | .1  | OVERVIEW                                           | 21  |

| 5  | .2  | DOCUMENTATION OF MAPPING TO APIS                   | 21  |

| 5  | .3  | COMPATIBILITY WITH UNSPECIFIED NATIVE ACTIONS      | 21  |

| 5  | .4  | MAPPING TO NATIVE INTERFACES                       | 21  |

| 6  | со  | MMON PROGRAMMING MODEL BEHAVIOR                    | 22  |

| 6  | 5.1 | OVERVIEW                                           | 22  |

| 6  | .2  | CONFORMANCE TO MULTIPLE FILE MODES                 | 22  |

| 6  | .3  | DEVICE STATE AT SYSTEM STARTUP                     | 22  |

| 6  | .4  | Secure erase                                       | 22  |

| 6  | .5  | ALLOCATION OF SPACE                                | 22  |

| 6  | .6  | INTERACTION WITH I/O DEVICES                       | 22  |

| 6  | .7  | NVM STATE AFTER A MEDIA OR CONNECTION FAILURE      | 23  |

|    |     | rogramming Model (NPM) SNIA Technical Position     | 5   |

| 6.8                                                     | ERROR HANDLING FOR PERSISTENT MEMORY         | 23                                           |

|---------------------------------------------------------|----------------------------------------------|----------------------------------------------|

| 6.9                                                     | PERSISTENCE DOMAIN                           | 23                                           |

| 6.10                                                    | ALIGNED OPERATIONS ON FUNDAMENTAL DATA TYPES | 23                                           |

| 6.11                                                    | COMMON ACTIONS                               | 24                                           |

| 6.12                                                    | COMMON ATTRIBUTES                            | 25                                           |

| 6.13                                                    | USE CASES                                    | 25                                           |

| 7 N\                                                    | /M.BLOCK MODE                                | 27                                           |

| 7.1                                                     | OVERVIEW                                     | 27                                           |

| 7.2                                                     | ACTIONS                                      | 29                                           |

| 7.3                                                     | ATTRIBUTES                                   | 32                                           |

| 7.4                                                     | USE CASES                                    | 36                                           |

| 8 N\                                                    | /M.FILE MODE                                 | 40                                           |

| 8.1                                                     | OVERVIEW                                     | 40                                           |

| 8.2                                                     | ACTIONS                                      | 40                                           |

|                                                         |                                              |                                              |

| 8.3                                                     | Attributes                                   | 42                                           |

| 8.3<br>8.4                                              | Attributes                                   |                                              |

| 8.4                                                     |                                              | 43                                           |

| 8.4                                                     | USE CASES                                    | 43<br><b>50</b>                              |

| 8.4<br>9 NV                                             | Use cases                                    | 43<br><b>50</b><br>50                        |

| 8.4<br><b>9 NV</b><br>9.1                               | Use cases                                    | 43<br><b>50</b><br>50                        |

| 8.4<br>9 NV<br>9.1<br>9.2<br>9.3                        | Use cases                                    | 43<br><b>50</b><br>50<br>53                  |

| 8.4<br>9 NV<br>9.1<br>9.2<br>9.3<br>9.4                 | Use cases                                    | 43<br><b>50</b><br>50<br>53<br>55            |

| 8.4<br>9 NV<br>9.1<br>9.2<br>9.3<br>9.4                 | USE CASES                                    | 43<br>50<br>50<br>53<br>55<br><b>58</b>      |

| 8.4<br>9 NV<br>9.1<br>9.2<br>9.3<br>9.4<br>10 N         | USE CASES                                    | 43<br>50<br>50<br>53<br>55<br>55<br>58<br>58 |

| 8.4<br>9 NV<br>9.1<br>9.2<br>9.3<br>9.4<br>10 N<br>10.1 | USE CASES                                    | 43<br>50<br>50<br>53<br>55<br>58<br>58<br>61 |

| ANNEX | ΧA   | (INFORMATIVE) PM POINTERS           | 78 |

|-------|------|-------------------------------------|----|

| ANNEX | КΒ   | (INFORMATIVE) PM ERROR HANDLING     | 79 |

| ANNEX | ХC   | (INFORMATIVE) DEFERRED BEHAVIOR     | 83 |

| D.1   | Remo | DTE SHARING OF NVM                  | 83 |

| D.2   | MAP  | _CACHED OPTION FOR NVM.PM.FILE.MAP  | 83 |

| D.3   | NVM  | .PM.FILE.DURABLE.STORE              | 83 |

| D.4   | Ενη  | NCED NVM.PM.FILE.WRITE              | 83 |

| D.5   | Mana | AGEMENT-ONLY BEHAVIOR               | 83 |

| D.6   | Acce | ESS HINTS                           | 83 |

| D.7   | Μυιτ | TI-DEVICE ATOMIC MULTI-WRITE ACTION | 83 |

| D.8   | NVM  | BLOCK.DISCARD_IF_YOU_MUST ACTION    | 83 |

| D.9   | Ατοι | IC WRITE ACTION WITH ISOLATION      | 85 |

| D.10  | Ато  | OMIC SYNC/FLUSH ACTION FOR PM       | 85 |

| D.11  | HA   | RDWARE-ASSISTED VERIFY              | 85 |

# Table of Figures

| 16 |

|----|

| 16 |

| 16 |

| 17 |

| 18 |

| 27 |

| 36 |

| 37 |

| 37 |

| 40 |

| 50 |

| 54 |

| 54 |

| 58 |

| 81 |

|    |

## FOREWORD

The SNIA NVM Programming Technical Working Group was formed to address the ongoing proliferation of new non-volatile memory (NVM) functionality and new NVM technologies. An extensible NVM Programming Model is necessary to enable an industry wide community of NVM producers and consumers to move forward together through a number of significant storage and memory system architecture changes.

This SNIA specification defines recommended behavior between various user space and operating system (OS) kernel components supporting NVM. This specification does not describe a specific API. Instead, the intent is to enable common NVM behavior to be exposed by multiple operating system specific interfaces.

After establishing context, the specification describes several operational modes of NVM access. Each mode is described in terms of use cases, actions and attributes that inform user and kernel space components of functionality that is provided by a given compliant implementation.

#### Acknowledgements

The SNIA NVM Programming Technical Working Group, which developed and reviewed this standard, would like to recognize the significant contributions made by the following members:

Organization Represented EMC Hewlett Packard NetApp Hewlett Packard Fusion-io Red Hat Fusion-io Rougs, LLC Intel Corporation Microsoft Fusion-io Hewlett Packard Intel Corporation Name of Representative Bob Beauchamp Hans Boehm Steve Byan Joe Foster Walt Hubis Jeff Moyer Ned Plasson Tony Roug Andy Rudoff Spencer Shepler Nisha Talagata Doug Voigt Paul von Behren

# 1 Scope

This specification is focused on the points in system software where NVM is exposed either as a hardware abstraction within an operating system kernel (e.g., a volume) or as a data abstraction (e.g., a file) to user space applications. The technology that motivates this specification includes flash memory packaged as solid state disks and PCI cards as well as other solid state non-volatile devices, including those which can be accessed as memory.

It is not the intent to exhaustively describe or in any way deprecate existing modes of NVM access. The goal of the specification is to augment the existing common storage access models (e.g., volume and file access) to add new NVM access modes. Therefore this specification describes the discovery and use of capabilities of NVM media, connections to the NVM, and the system containing the NVM that are emerging in the industry as vendor specific implementations. These include:

- supported access modes,

- visibility in memory address space,

- atomicity and durability,

- recognizing, reporting, and recovering from errors and failures,

- data granularity, and

- capacity reclamation.

This revision of the specification focuses on NVM behaviors that enable user and kernel space software to locate, access, and recover data. It does not describe behaviors that are specific to administrative or diagnostic tasks for NVM. There are several reasons for intentionally leaving administrative behavior out of scope.

- For new types of storage programming models, the access must be defined and agreed on before the administration can be defined. Storage management behavior is typically defined in terms of how it enables and diagnoses the storage programming model.

- Administrative tasks often require human intervention and are bound to the syntax for the administration. This document does not define syntax. It focuses only on the semantics of the programming model.

- Defining diagnostic behaviors (e.g., wear-leveling) as vendor-agnostic is challenging across all vendor implementations. A common recommended behavior may not allow an approach optimal for certain hardware.

This revision of the specification does not address sharing data across computing nodes. This revision of the specification assumes that sharing data between processes and threads follows the native OS and hardware behavior.

# 2 References

The following referenced documents are indispensable for the application of this document.

For references available from ANSI, contact ANSI Customer Service Department at (212) 642-49004980 (phone), (212) 302-1286 (fax) or via the World Wide Web at http://www.ansi.org.

| SPC-3            | ISO/IEC 14776-453, SCSI Primary Commands – 3 [ANSI INCITS 408-<br>2005]                                                                                                                                                                          |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | Approved standard, available from ANSI.                                                                                                                                                                                                          |

| SBC-2            | ISO/IEC 14776-322, SCSI Block Commands - 2 [T10/BSR INCITS 514]                                                                                                                                                                                  |

|                  | Approved standard, available from ANSI.                                                                                                                                                                                                          |

| ACS-2            | ANSI INCITS 482-2012, Information technology - ATA/ATAPI Command Set -2                                                                                                                                                                          |

|                  | Approved standard, available from ANSI.                                                                                                                                                                                                          |

| NVMe 1.1         | NVM Express Revision 1.1,                                                                                                                                                                                                                        |

|                  | Approved standard, available from <a href="http://nvmexpress.org">http://nvmexpress.org</a>                                                                                                                                                      |

| SPC-4            | SO/IEC 14776-454, SCSI Primary Commands - 4 (SPC-4) (T10/1731-D)                                                                                                                                                                                 |

|                  | Under development, available from http://www.t10.org.                                                                                                                                                                                            |

| SBC-4            | ISO/IEC 14776-324, SCSI Block Commands - 4 (SBC-4) [BSR INCITS 506]                                                                                                                                                                              |

|                  | Under development, available from http://www.t10.org.                                                                                                                                                                                            |

| T10 13-<br>064r0 | T10 proposal 13-064r0, Rob Elliot, Ashish Batwara, SBC-4 SPC-5<br>Atomic writes                                                                                                                                                                  |

|                  | Proposal, available from http://www.t10.org.                                                                                                                                                                                                     |

| ACS-2 r7         | Information technology - ATA/ATAPI Command Set – 2 r7 (ACS-2)                                                                                                                                                                                    |

|                  | Under development, available from http://www.t13.org.                                                                                                                                                                                            |

| Intel SPG        | Intel Corporation, Intel 64 and IA-32 Architectures Software Developer's<br>Manual Combined Volumes 3A, 3B, and 3C: System Programming<br>Guide, Parts 1 and 2, available from<br>http://download.intel.com/products/processor/manual/325384.pdf |

|                  | mp.//download.mei.com/products/processor/manda//o20004.pdf                                                                                                                                                                                       |

# 3 Definitions, abbreviations, and conventions

For the purposes of this document, the following definitions and abbreviations apply.

# 3.1 Definitions

#### 3.1.1 durable

committed to a persistence domain (see 3.1.7)

#### 3.1.2 load and store operations

commands to move data between CPU registers and memory

#### 3.1.3 memory-mapped file

segment of virtual memory which has been assigned a direct byte-for-byte correlation with some portion of a file

#### 3.1.4 non-volatile memory

any type of memory-based, persistent media; including flash memory packaged as solid state disks, PCI cards, and other solid state non-volatile devices

#### 3.1.5 NVM block capable driver

driver supporting the native operating system interfaces for a block device

#### 3.1.6 NVM volume

subset of one or more NVM devices, treated by software as a single logical entity

See 4.2 NVM device models

#### 3.1.7 persistence domain

location for data that is guaranteed to preserve the data contents across a restart of the device containing the data

See 6.9 Persistence domain

#### 3.1.8 persistent memory

storage technology with performance characteristics suitable for a load and store programming model

#### 3.1.9 programming model

set of software interfaces that are used collectively to provide an abstraction for hardware with similar capabilities

## 3.2 Keywords

In the remainder of the specification, the following keywords are used to indicate text related to compliance:

#### 3.2.1 mandatory

a keyword indicating an item that is required to conform to the behavior defined in this standard

#### 3.2.2 may

a keyword that indicates flexibility of choice with no implied preference; "may" is equivalent to "may or may not"

#### 3.2.3 may not

keywords that indicate flexibility of choice with no implied preference; "may not" is equivalent to "may or may not"

#### 3.2.4 need not

keywords indicating a feature that is not required to be implemented; "need not" is equivalent to "is not required to"

#### 3.2.5 optional

a keyword that describes features that are not required to be implemented by this standard; however, if any optional feature defined in this standard is implemented, then it shall be implemented as defined in this standard

#### 3.2.6 **shall**

a keyword indicating a mandatory requirement; designers are required to implement all such mandatory requirements to ensure interoperability with other products that conform to this standard

#### 3.2.7 **should**

a keyword indicating flexibility of choice with a strongly preferred alternative

## 3.3 Abbreviations

ACID Atomicity, Consistency, Isolation, Durability

NVM Non-Volatile Memory

- PM Persistent Memory

- SSD Solid State Disk

## 3.4 Conventions

#### Representation of modes in figures

Modes are represented by red, wavy lines in figures, as shown below:

The wavy lines have labels identifying the mode name (which in turn, identifies a clause of the specification).

# 4 Overview of the NVM Programming Model (informative)

# 4.1 How to read and use this specification

Documentation for I/O programming typically consists of a set of OS-specific Application Program Interfaces (APIs). API documentation describes the syntax and behavior of the API. This specification intentionally takes a different approach and describes the behavior of NVM programming interfaces, but allows the syntax to integrate with similar operating system interfaces. A recommended approach for using this specification is:

1. Determine which mode applies (read 4.3 NVM programming modes).

2. Refer to the mode section to learn about the functionality provided by the mode and how it relates to native operating system APIs; the use cases provide examples. The mode specific section refers to other specification sections that may be of interest to the developer.

3. Determine which mode actions and attributes relate to software objectives.

4. Locate the vendor/OS mapping document (see 5.2) to determine which APIs map to the actions and attributes.

For an example, a developer wants to update an existing application to utilize persistent memory hardware. The application is designed to bypass caches to assure key content is durable across power failures; the developer wants to learn about the persistent memory programming model. For this example:

1. The NVM programming modes section identifies NVM.PM.FILE mode (see 10 NVM.PM.FILE) as the starting point for application use of persistent memory.

2. The NVM.PM.FILE mode text describes the general approach for accessing PM (similar to native memory-mapped files) and the role of PM aware file system.

3. The NVM.PM.FILE mode identifies the NVM.PM.FILE.MAP and NVM.PM.FILE.SYNC actions and attributes that allow an application to discover support for optional features.

4. The operating system vendor's mapping document describes the mapping between NVM.PM.FILE.MAP/SYNC and API calls, and also provides information about supported PM-aware file systems.

# 4.2 NVM device models

### 4.2.1 Overview

This section describes device models for NVM to help readers understand how key terms in the programming model relate to other software and hardware. The models presented here generally apply across operating systems, file systems, and hardware; but there are differences across implementations. This specification strives to discuss the model generically, but mentions key exceptions.

One of the challenges discussing the software view of NVM is that the same terms are often used to mean different things. For example, between commonly used management applications, programming interfaces, and operating system documentation, *volume* may refer to a variety of things. Within this specification, *NVM volume* has a specific meaning.

An NVM volume is a subset of one or more NVM devices, treated by software as a single logical entity. For the purposes of this specification, a volume is a container of storage. A volume may be block capable and may be persistent memory capable. The consumer of a volume sees its content as a set of contiguous addresses, but the unit of access for a volume differs across different modes and device types. Logical addressability and physical allocation may be different.

In the examples in this section, "NVM block device" refers to NVM hardware that emulates a disk and is accessed in software by reading or writing ranges of blocks. "PM device" refers to NVM hardware that may be accessed via load and store operations.

#### 4.2.2 Block NVM example

Consider a single drive form factor SSD where the entire SSD capacity is dedicated to a file system. In this case, a single NVM block volume maps to a single hardware device. A file system (not depicted) is mounted on the NVM block volume.

The same model may apply to NVM block hardware other than an SDD (including flash on PCIe cards).

#### 4.2.3 Persistent memory example

This example depicts a NVDIMM and PM volume. A PM-aware file system (not depicted) would be mounted on the PM volume.

The same model may apply to PM hardware other than an NVDIMM (including SSDs, PCIe cards, etc.).

#### 4.2.4 NVM block volume using PM hardware

In this example, the persistent memory implementation includes a driver that uses a range of persistent memory (a PM volume) and makes it appear to be a block NVM device in the legacy block stack. This emulated block device could be aggregated or de-aggregated like legacy block devices. In this example, the

emulated block device is mapped 1-1 to an NVM block volume and non-PM file system.

Note that there are other models for connecting a non-PM file system to PM hardware.

Figure 1 Block NVM example

NVM block volume

SSD hardware

#### Figure 3 Block volume using PM HW

| NVM block volume |  |  |

|------------------|--|--|

|                  |  |  |

| PM volume        |  |  |

| PM hardware      |  |  |

# 4.3 NVM programming modes

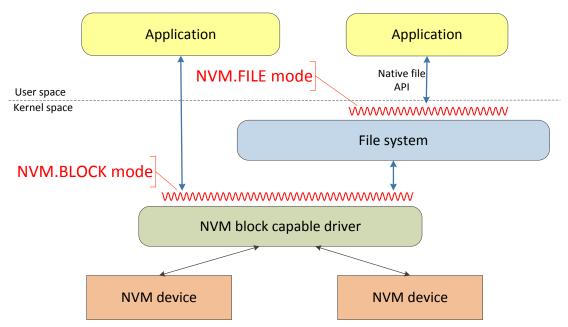

### 4.3.1 NVM.BLOCK mode overview

NVM.BLOCK and NVM.FILE modes are used when NVM devices provide block storage behavior to software (in other words, emulation of hard disks). The NVM may be exposed as a single or as multiple NVM volumes. Each NVM volume supporting these modes provides a range of logically-contiguous blocks. NVM.BLOCK mode is used by operating system components (for example, file systems) and by applications that are aware of block storage characteristics and the block addresses of application data.

This specification does not document existing block storage software behavior; the NVM.BLOCK mode describes NVM extensions including:

- Discovery and use of atomic write and discard features

- The discovery of granularities (length or alignment characteristics)

- Discovery and use of ability for applications or operating system components to mark blocks as unreadable

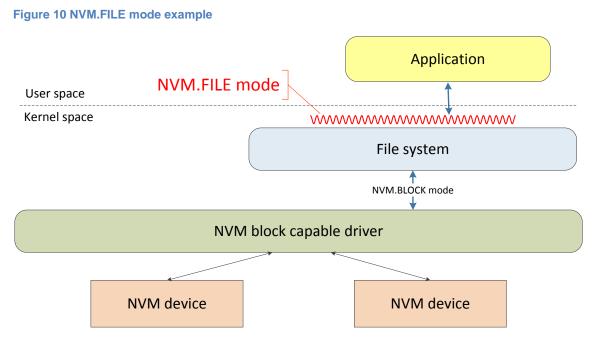

Figure 4 NVM.BLOCK and NVM.FILE mode examples

#### 4.3.2 NVM.FILE mode overview

NVM.FILE mode is used by applications that are not aware of details of block storage hardware or addresses. Existing applications written using native file I/O behavior should work unmodified with NVM.FILE mode; adding support in the application for NVM extensions may optimize the application.

An application using NVM.FILE mode may or may not be using memory-mapped file I/O behavior.

The NVM.FILE mode describes NVM extensions including:

- Discovery and use of atomic write features

- The discovery of granularities (length or alignment characteristics)

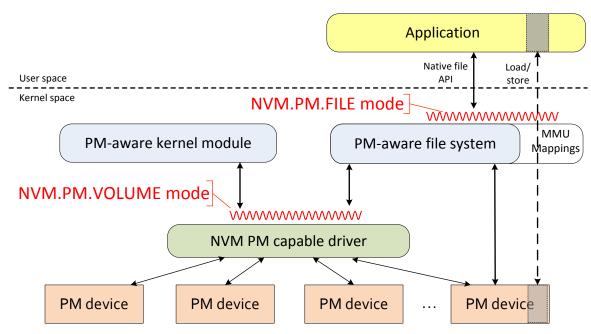

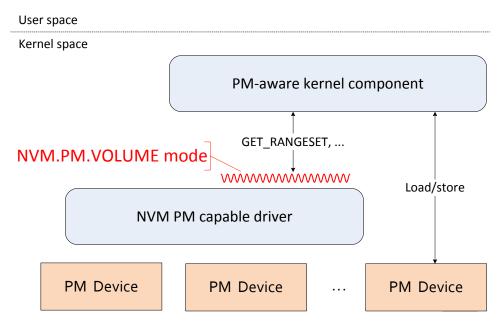

#### 4.3.3 NVM.PM.VOLUME mode overview

NVM.PM.VOLUME mode describes the behavior for operating system components (such as file systems) accessing persistent memory. NVM.PM.VOLUME mode provides a software abstraction for Persistent Memory hardware and profiles functionality for operating system components including:

• the list of physical address ranges associated with each PM volume

#### Figure 5 NVM.PM.VOLUME and NVM.PM.FILE mode examples

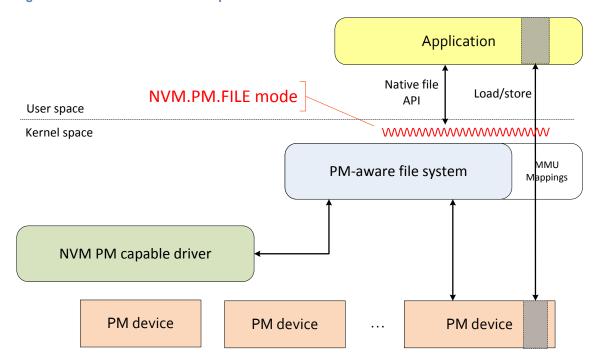

#### 4.3.4 NVM.PM.FILE mode overview

NVM.PM.FILE mode describes the behavior for applications accessing persistent memory. The commands implementing NVM.PM.FILE mode are similar to those using NVM.FILE mode, but NVM.PM.FILE mode may not involve I/O to the page cache. NVM.PM.FILE mode documents behavior including:

- mapping PM files (or subsets of files) to virtual memory addresses

- syncing portions of PM files to the persistence domain

## 4.4 Introduction to actions, attributes, and use cases

#### 4.4.1 Overview

This specification uses four types of elements to describe NVM behavior. Use cases are the highest order description. They describe complete scenarios that accomplish a goal. Actions are more specific in that they describe an operation that represents or interacts with NVM. Attributes comprise information about NVM. Property Group Lists describe groups of related properties that may be considered attributes of a data structure or class; but the specification allows flexibility in the implementation.

#### 4.4.2 Use cases

In general, a use case states a goal or trigger and a result. It captures the intent of an application and describes how actions are used to accomplish that intent. Use cases illustrate the use of actions and help to validate action definitions. Use cases also describe system behaviors that are not represented as actions. Each use case includes the following information:

- a purpose and context including actors involved in the use case;

- triggers and preconditions indicating when a use case applies;

- inputs, outputs, events and actions that occur during the use case;

- references to related materials or concepts including other use cases that use or extend the use case.

#### 4.4.3 Actions

Actions are defined using the following naming convention:

#### <context>.<mode>.<verb>

The actions in this specification all have a context of "NVM". The mode refers to one of the NVM models documented herein (or "COMMON" for actions used in multiple modes). The verb states what the action does. Examples of actions include "NVM.COMMON.GET\_ATTRIBUTE" and "NVM.FILE.ATOMIC\_WRITE". In some cases native actions that are not explicitly specified by the programming model are referenced to illustrate usage.

The description of each action includes:

- parameters and results of the action

- details of the action's behavior

- compatibility of the action with pre-existing APIs in the industry

A number of actions involve options that can be specified each time the action is used. The options are given names that begin with the name of the action and end with a descriptive term that is unique for the action. Examples include NVM.PM.FILE.MAP\_COPY\_ON\_WRITE and NVM.PM.FILE.MAP\_SHARED.

A number of actions are optional. For each of these, there is an attribute that indicates whether the action is supported by the implementation in question. By convention these attributes end with the term "CAPABLE" such as NVM.BLOCK.ATOMIC\_WRITE\_CAPABLE. Supported options are also enumerated by attributes that end in "CAPABLE".

### 4.4.4 Attributes

Attributes describe properties or capabilities of a system. This includes indications of which actions can be performed in that system and variations on the internal behavior of specific actions. For example attributes describe which NVM modes are supported in a system, and the types of atomicity guarantees available.

In this programming model, attributes are not arbitrary key value pairs that applications can store for unspecified purposes. Instead the NVM attributes are intended to provide a common way to discover and configure certain aspects of systems based on agreed upon interpretations of names and values. While this can be viewed as a key value abstraction it does not require systems to implement a key value repository. Instead, NVM attributes are mapped to a system's native means of describing and configuring those aspects associated with said attributes. Although this specification calls out a set of attributes, the intent is to allow attributes to be extended in vendor unique ways through a process that enables those extensions to become attributes and/or attribute values in a subsequent version of the specification or in a vendor's mapping document.

#### 4.4.5 **Property group lists**

A **property group** is set of property values used together in lists; typically **property group lists** are inputs or outputs to actions. The implementation may choose to implement a property group as a new data structure or class, use properties in existing data structures or classes, or other mechanisms as long as the caller can determine which collection of values represent the members of each list element.

# 5 Compliance to the programming model

# 5.1 Overview

Since a programming model is intentionally abstract, proof of compliance is somewhat indirect. The intent is that a compliant implementation, when properly configured, can be used in such a way as to exhibit the behaviors described by the programming model without unnecessarily impacting other aspects of the implementation.

Compliance of an implementation shall be interpreted as follows.

# 5.2 Documentation of mapping to APIs

In order to be considered compliant with this programming model, implementations must provide documentation of the mapping of attributes and actions in the programming model to their counterparts in the implementation.

# 5.3 Compatibility with unspecified native actions

Actions and attributes of the native block and file access methods that correspond to the modes described herein shall continue to function as defined in those native methods. This specification does not address unmodified native actions except in passing to illustrate their usage.

# 5.4 Mapping to native interfaces

Implementations are expected to provide the behaviors specified herein by mapping them as closely as possible to native interfaces. An implementation is not required to have a one-to-one mapping between actions (or attributes) and APIs – for example, an implementation may have an API that implements multiple actions.

NVM Programming Model action descriptions do not enumerate all possible results of each action. Only those that modify programming model specific behavior are listed. The results that are referenced herein shall be discernible from the set of possible results returned by the native action in a manner that is documented with action mapping.

Attributes with names ending in \_CAPABLE are used to inform a caller whether an optional action or attribute is supported by the implementations. The mandatory requirement for \_CAPABLE attributes can be met by the mapping document describing the implementation's default behavior for reporting unsupported features. For example: the mapping document could state that if a flag with a name based on the attribute is undefined, then the action/attribute is not supported.

# 6 Common programming model behavior

# 6.1 Overview

This section describes behavior that is common to multiple modes and also behavior that is independent from the modes.

# 6.2 Conformance to multiple file modes

A single computer system may include implementations of both NVM.FILE and NVM.PM.FILE modes. A given file system may be accessed using either or both modes provided that the implementations are intended by their vendor(s) to interoperate. Each implementation shall specify its own mapping to the NVM Programming Model.

A single file system implementation may include both NVM.FILE and NVM.PM.FILE modes. The mapping of the implementation to the NVM Programming Model must describe how the actions and attributes of different modes are distinguished from one another.

Implementation specific errors may result from attempts to use NVM.PM.FILE actions on files that were created in NVM.FILE mode or vice versa. The mapping of each implementation to the NVM Programming Model shall specify any limitations related multi-mode access.

# 6.3 Device state at system startup

Prior to use, a file system is associated with one or more volumes and/or NVM devices.

The NVM devices shall be in a state appropriate for use with file systems. For example, if transparent RAID is part of the solution, components implementing RAID shall be active so the file system sees a unified virtual device rather than individual RAID components.

# 6.4 Secure erase

Secure erase of a volume or device is an administrative act with no defined programming model action.

# 6.5 Allocation of space

Following native operating system behavior, this programming model does not define specific actions for allocating space. Most allocation behavior is hidden from the user of the file, volume or device.

# 6.6 Interaction with I/O devices

Interaction between Persistent Memory and I/O devices (for example, DMA) shall be consistent with native operating system interactions between devices and volatile memory.

# 6.7 NVM State after a media or connection failure

There is no action defined to determine the state of NVM for circumstances such as a media or connection failure. Vendors may provide techniques such as redundancy algorithms to address this, but the behavior is outside the scope of the programming model.

# 6.8 Error handling for persistent memory

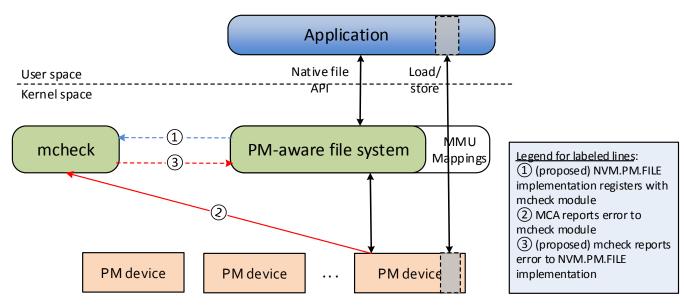

The handling of errors in memory-mapped file implementations varies across operating systems. Existing implementations support memory error reporting however there is not sufficient similarity for a uniform approach to persistent memory error handling behavior. Additional work is required to define an error handling approach. The following factors are to be taken into account when dealing with errors.

- The application is in the best position to perform recovery as it may have access to additional sources of data necessary to rewrite a bad memory address.

- Notification of a given memory error occurrence may need to be delivered to both kernel and user space consumers (e.g., file system and application)

- Various hardware platforms have different capabilities to detect and report memory errors

- Attributes and possibly actions related to error handling behavior are needed in the NVM Programming model

A proposal for persistent memory error handling appears as an appendix; see Annex B.

# 6.9 Persistence domain

NVM PM hardware supports the concept of a persistence domain. Once data has reached a persistence domain, it may be recoverable during a process that results from a system restart. Recoverability depends on whether the pattern of failures affecting the system during the restart can be tolerated by the design and configuration of the persistence domain.

Multiple persistence domains may exist within the same system. It is an administrative act to align persistence domains with volumes and/or file systems. This must be done in such a way that NVM Programming Model behavior is assured from the point of view of each compliant volume or file system.

# 6.10 Aligned operations on fundamental data types

Data alignment means putting the data at a memory offset equal to some multiple of the word size, which increases the system's performance due to the way the CPU handles memory (from Wikipedia "Data structure alignment"). Data types are *fundamental* when they are native to programming languages or libraries.

Aligned operations on data types are usually exactly the same operations that under normal operation become visible to other threads/data producers atomically. They are already well-defined for most settings:

- Instruction Set Architectures already define them.

- E.g., for x86, MOV instructions with naturally aligned operands of at most 64 bits qualify.

- They're generated by known high-level language constructs, e.g.:

- C++11 lock-free atomic<T>, C11 \_Atomic(T), Java & C# volatile, OpenMP atomic directives.

For optimal performance, fundamental data types fit within CPU cache lines.

## 6.11 Common actions

#### 6.11.1 NVM.COMMON.GET\_ATTRIBUTE

Requirement: mandatory

Get the value of one or more attributes. Implementations conforming to the specification shall provide the get attribute behavior, but multiple programmatic approaches may be used.

#### Inputs:

- reference to appropriate instance (for example, reference to an NVM volume)

- attribute name

#### Outputs:

• value of attribute

The vendor's mapping document shall describe the possible errors reported for all applicable programmatic approaches.

#### 6.11.2 NVM.COMMON.SET\_ATTRIBUTE

Requirement: optional

Note: at this time, no settable attributes are defined in this specification, but they may be added in a future revision.

Set the value of one attribute. Implementations conforming to the specification shall provide the set attribute behavior, but multiple programmatic approaches may be used.

#### Inputs:

- reference to appropriate instance

- attribute name

- value to be assigned to the attribute

The vendor's mapping document shall describe the possible errors reported for all applicable programmatic approaches.

## 6.12 Common attributes

#### 6.12.1 NVM.COMMON.SUPPORTED\_MODES

Requirement: mandatory

SUPPORTED\_MODES returns a list of the modes supported by the NVM implementation.

Possible values: NVM.BLOCK, NVM.FILE, NVM.PM.FILE, NVM.PM.VOLUME

NVM.COMMON.SET\_ATTRIBUTE is not supported for NVM.COMMON.SUPPORTED\_MODES.

#### 6.12.2 NVM.COMMON.FILE\_MODE

Requirement: mandatory if NVM.FILE or NVM.PM.FILE is supported

Returns the supported file modes (NVM.FILE and/or NVM.PM.FILE) provided by a file system.

Target: a file path

Output value: a list of values: "NVM.FILE" and/or "NVM.PM.FILE"

See 6.2 Conformance to multiple file modes.

#### 6.13 Use cases

#### 6.13.1 Application determines which mode is used to access a file system

#### Purpose/triggers:

An application needs to determine whether the underlying file system conforms to NVM.FILE mode, NVM.PM.FILE mode, or both.

#### Scope/context:

Some actions and attributes are defined differently in NVM.FILE and NVM.PM.FILE; applications may need to be designed to handle these modes differently. This use case describes steps in an application's initialization logic to determine the mode(s) supported by the implementation and set a variable indicating the preferred mode the application will use in subsequent actions. This application prefers to use NVM.PM.FILE behavior if both modes are supported.

#### Success scenario:

- 1) Invoke NVM.COMMON.GET\_ATTRIBUTE (NVM.COMMON.FILE\_MODE) targeting a file path; the value returned provides information on which modes may be used to access the data.

- If the response includes "NVM.FILE", then the actions and attributes described for the NVM.FILE mode are supported. Set the preferred mode for this file system to NVM.FILE.

3) If the response includes "NVM.PM.FILE", then the actions and attributes described for the NVM.PM.FILE mode are supported. Set the preferred mode for this file system to NVM.PM.FILE.

#### **Outputs:**

#### **Postconditions:**

A variable representing the preferred mode for the file system has been initialized.

See also:

6.2 Conformance to multiple file modes 6.12.2 NVM.COMMON.FILE\_MODE

# 7 NVM.BLOCK mode

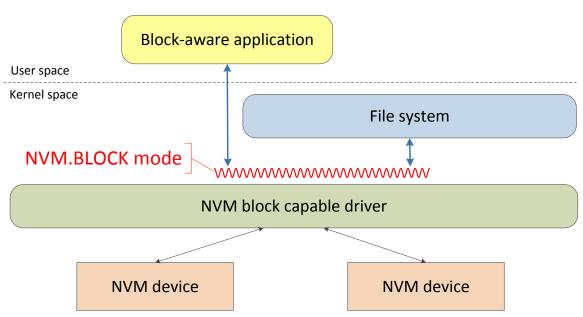

## 7.1 Overview

NVM.BLOCK mode provides programming interfaces for NVM implementations behaving as block devices. The programming interfaces include the native operating system behavior for sending I/O commands to a block driver and adds NVM extensions. To support this mode, the NVM devices are supported by an NVM block capable driver that provides the command interface to the NVM. This specification does not document the native operating system block programming capability; it is limited to the NVM extensions.

Figure 6 NVM.BLOCK mode example

Support for NVM.BLOCK mode requires that the NVM implementation support all behavior not covered in this section consistently with the native operating system behavior for native block devices.

The NVM extensions supported by this mode include:

- Discovery and use of atomic write and discard features

- The discovery of granularities (length or alignment characteristics)

- Discovery and use of per-block metadata used for verifying integrity

- Discovery and use of ability for applications or operating system components to mark blocks as unreadable

#### 7.1.1 Discovery and use of atomic write features

Atomic Write support provides applications with the capability to assure that all the data for an operation is written to the persistence domain or, if a failure occurs, it appears that no operation took place. Applications may use atomic write operations to assure consistent

behavior during a failure condition or to assure consistency between multiple processes accessing data simultaneously.

### 7.1.2 The discovery of granularities

Attributes are introduced to allow applications to discover granularities associated with NVM devices.

#### 7.1.3 Discovery and use of capability to mark blocks as unreadable

An action (NVM.BLOCK.SCAR) is defined allowing an application to mark blocks as unreadable.

#### 7.1.4 NVM.BLOCK consumers: operating system and applications

NVM.BLOCK behavior covers two types of software: NVM-aware operating system components and block-optimized applications.

#### 7.1.4.1 NVM.BLOCK operating system components

NVM-aware operating system components use block storage and have been enhanced to take advantage of NVM features. Examples include file systems, logical volume managers, software RAID, and hibernation logic.

#### 7.1.4.2 Block-optimized applications

Block-optimized applications use a hybrid behavior utilizing files and file I/O operations, but construct file I/O commands in order to cause drivers to issue desired block commands. Operating systems and file systems typically provide mechanisms to enable block-optimized application. The techniques are system specific, but may include:

- A mechanism for a block-optimized application to request that the file system move data directly between the device and application memory, bypassing the buffering typically provided by the file system.

- The operating system or file system may require the application to align requests on block boundaries.

The file system and operating system may allow block-optimized applications to use memorymapped files.

#### 7.1.4.3 Mapping documentation

NVM.BLOCK operating system components may use I/O commands restricted to kernel space to send I/O commands to drivers. NVM.BLOCK applications may use a constrained set of file I/O operations to send commands to drivers. As applicable, the implementation shall provide documentation mapping actions and/or attributes for all supported techniques for NVM.BLOCK behavior.

The implementation shall document the steps to utilize supported capabilities for blockoptimized applications and the constraints (e.g., block alignment) compared to NVM.FILE behavior.

# 7.2 Actions

#### 7.2.1 Actions that apply across multiple modes

The following actions apply to NVM.BLOCK mode as well as other modes. NVM.COMMON.GET\_ATTRIBUTE (see 6.11.1) NVM.COMMON.SET\_ATTRIBUTE (see 6.11.2)

#### 7.2.2 NVM.BLOCK.ATOMIC\_WRITE

Requirement: mandatory if ATOMIC\_WRITE\_CAPABLE (see 7.3.1) is true

Block-optimized applications or operating system components may use ATOMIC\_WRITE to assure consistent behavior during a power failure condition. This specification does not specify the order in which this action occurs relative to other I/O operations, including other ATOMIC\_WRITE or ATOMIC\_MULTIWRITE actions. This specification does not specify when the data written becomes visible to other threads.

#### Inputs:

- the starting memory address

- a reference to the block device

- the starting block address

- the length

The interpretation of addresses and lengths (block or byte, alignment) should be consistent with native write actions. Implementations shall provide documentation on the requirements for specifying the starting addresses, block device, and length.

#### **Return values:**

- Success shall be returned if all blocks are updated in the persistence domain

- an error shall be reported if the length exceeds ATOMIC\_WRITE\_MAX\_DATA\_LENGTH (see 7.3.3)

- an error shall be reported if the starting address is not evenly divisible by ATOMIC\_WRITE\_STARTING\_ADDRESS\_GRANULARITY (see 7.3.4)

- an error shall be reported if the length is not evenly divisible by ATOMIC\_WRITE\_LENGTH\_GRANULARITY (see 7.3.5)

- If anything does or will prevent all of the blocks from being updated in the persistence domain before completion of the operation, an error shall be reported and all the logical blocks affected by the operation shall contain the data that was present before the device server started processing the write operation (i.e., the old data, as if the atomic write operation had no effect). If the NVM and processor are both impacted by a power failure, no error will be returned since the execution context is lost.

- the different errors described above shall be discernible by the consumer and shall be discernible from media errors

#### Relevant attributes:

ATOMIC\_WRITE\_MAX\_DATA\_LENGTH (see 7.3.3)

ATOMIC\_WRITE\_STARTING\_ADDRESS\_GRANULARITY (see 7.3.4) ATOMIC\_WRITE\_LENGTH\_GRANULARITY (see 7.3.5) ATOMIC\_WRITE\_CAPABLE (see 7.3.1)

### 7.2.3 NVM.BLOCK.ATOMIC\_MULTIWRITE

Requirement: mandatory if ATOMIC\_MULTIWRITE\_CAPABLE (see 7.3.6) is true

Block-optimized applications or operating system components may use ATOMIC\_MULTIWRITE to assure consistent behavior during a power failure condition. This action allows a caller to write non-adjacent extents atomically. The caller of ATOMIC\_MULTIWRITE provides a Property Group List (see 4.4.5) where the properties describe the memory and block extents (see Inputs below); all of the extents are written as a single atomic operation. This specification does not specify the order in which this action occurs relative to other I/O operations, including other ATOMIC\_WRITE or ATOMIC\_MULTIWRITE actions. This specification does not specify when the data written becomes visible to other threads.

#### Inputs:

A Property Group List (see 4.4.5) where the properties are:

- memory address starting address

- length of data to write (in bytes)

- a reference to the device being written to

- the starting LBA on the device

Each property group represents an I/O. The interpretation of addresses and lengths (block or byte, alignment) should be consistent with native write actions. Implementations shall provide documentation on the requirements for specifying the ranges.

#### Return values:

- Success shall be returned if all block ranges are updated in the persistence domain

- an error shall be reported if the block ranges overlap

- an error shall be reported if the total size of memory input ranges exceeds ATOMIC\_MULTIWRITE\_MAX\_DATA\_LENGTH (see 7.3.8)

- an error shall be reported if the starting address in any input memory range is not evenly divisible by ATOMIC\_MULTIWRITE\_STARTING\_ADDRESS\_GRANULARITY (see 7.3.9)

- an error shall be reported if the length in any input range is not evenly divisible by ATOMIC\_MULTIWRITE\_LENGTH\_GRANULARITY (see 7.3.10)

- If anything does or will prevent all of the writes from being applied to the persistence domain before completion of the operation, an error shall be reported and all the logical blocks affected by the operation shall contain the data that was present before the device server started processing the write operation (i.e., the old data, as if the atomic write operation had no effect). If the NVM and processor are both impacted by a power failure, no error will be returned since the execution context is lost.

- the different errors described above shall be discernible by the consumer

#### Relevant attributes:

ATOMIC\_MULTIWRITE\_MAX\_IOS (see 7.3.7) ATOMIC\_MULTIWRITE\_MAX\_DATA\_LENGTH (see 7.3.8) ATOMIC\_MULTIWRITE\_STARTING\_ADDRESS\_GRANULARITY (see 7.3.9) ATOMIC\_MULTIWRITE\_LENGTH\_GRANULARITY (see 7.3.10) ATOMIC\_MULTIWRITE\_CAPABLE (see 7.3.6)

#### 7.2.4 NVM.BLOCK.DISCARD\_IF\_YOU\_CAN

Requirement: mandatory if DISCARD\_IF\_YOU\_CAN\_CAPABLE (see 7.3.17) is true

This action notifies the NVM device that some or all of the blocks which constitute a volume are no longer needed by the application. This action is a hint to the device.

Although the application has logically discarded the data, it may later read this range. Since the device is not required to physically discard the data, its response is undefined: it may return successful response status along with unknown data (e.g., the old data, a default "undefined" data, or random data), or it may return an unsuccessful response status with an error.

Inputs: a range of blocks (starting LBA and length in logical blocks)

Status: Success indicates the request is accepted but not necessarily acted upon.

#### 7.2.5 NVM.BLOCK.DISCARD\_IMMEDIATELY

Requirement: mandatory if DISCARD\_IMMEDIATELY\_CAPABLE (see 7.3.18) is true

Requires that the data block be unmapped (see NVM.BLOCK.EXISTS 7.2.6) before the next READ or WRITE reference even if garbage collection of the block has not occurred yet,

DISCARD\_IMMEDIATELY commands cannot be acknowledged by the NVM device until the DISCARD\_IMMEDIATELY has been durably written to media in a way such that upon recovery from a power-fail event, the block is guaranteed to remain discarded.

Inputs: a range of blocks (starting LBA and length in logical blocks)

The values returned by subsequent read operations are specified by the DISCARD\_IMMEDIATELY\_RETURNS (see 7.3.19) attribute.

Status: Success indicates the request is completed.

See also EXISTS (7.2.6), DISCARD\_IMMEDIATELY\_RETURNS (7.3.19), DISCARD\_IMMEDIATELY\_CAPABLE (7.3.18).

#### 7.2.6 NVM.BLOCK.EXISTS

Requirement: mandatory if EXISTS\_CAPABLE (see 7.3.12) is true

An NVM device may allocate storage through a thin provisioning mechanism or one of the discard actions. As a result, a block can exist in one of three states:

- **Mapped**: the block has had data written to it

- Unmapped: the block has not been written, and there is no memory allocated

- Allocated: the block has not been written, but has memory allocated to it

The EXISTS action allows the NVM user to determine if a block has been allocated.

Inputs: an LBA

Output: the state (mapped, unmapped, or allocated) for the input block

Result: the status of the action

#### 7.2.7 NVM.BLOCK.SCAR

Requirement: mandatory if SCAR\_CAPABLE (see 7.3.13) is true

This action allows an application to request that subsequent reads from any of the blocks in the address range will cause an error. This action uses an implementation-dependent means to insure that all future reads to any given block from the scarred range will cause an error until new data is stored to any given block in the range. A block stays scarred until it is updated by a write operation.

Inputs: reference to a block volume, starting offset, length

Outputs: status

Relevant attributes:

NVM.BLOCK.SCAR\_CAPABLE (7.3.13) – Indicates that the SCAR action is supported.

## 7.3 Attributes

#### 7.3.1 Attributes that apply across multiple modes

The following attributes apply to NVM.BLOCK mode as well as other modes. NVM.COMMON.SUPPORTED\_MODES (see 6.12.1)

### 7.3.2 NVM.BLOCK.ATOMIC\_WRITE\_CAPABLE

Requirement: mandatory

This attribute indicates that the implementation is capable of the NVM.BLOCK.ATOMIC\_WRITE action.

## 7.3.3 NVM.BLOCK.ATOMIC\_WRITE\_MAX\_DATA\_LENGTH

Requirement: mandatory if ATOMIC\_WRITE\_CAPABLE (see 7.3.1) is true.

ATOMIC\_WRITE\_MAX\_DATA\_LENGTH is the maximum length of data that can be transferred by an ATOMIC\_WRITE action.

## 7.3.4 NVM.BLOCK.ATOMIC\_WRITE\_STARTING\_ADDRESS\_GRANULARITY

Requirement: mandatory if ATOMIC\_WRITE\_CAPABLE (see 7.3.1) is true.

ATOMIC\_WRITE\_STARTING\_ADDRESS\_GRANULARITY is the granularity of the starting memory address for an ATOMIC\_WRITE action. Address inputs to ATOMIC\_WRITE shall be evenly divisible by ATOMIC\_WRITE\_STARTING\_ADDRESS\_GRANULARITY.

### 7.3.5 NVM.BLOCK.ATOMIC\_WRITE\_LENGTH\_GRANULARITY

Requirement: mandatory if ATOMIC\_WRITE\_CAPABLE (see 7.3.1) is true.

ATOMIC\_WRITE\_LENGTH\_GRANULARITY is the granularity of the length of data transferred by an ATOMIC\_WRITE action. Length inputs to ATOMIC\_WRITE shall be evenly divisible by ATOMIC\_WRITE\_LENGTH\_GRANULARITY.

#### 7.3.6 NVM.BLOCK.ATOMIC\_MULTIWRITE\_CAPABLE

Requirement: mandatory

ATOMIC\_MULTIWRITE\_CAPABLE indicates that the implementation is capable of the NVM.BLOCK.ATOMIC\_MULTIWRITE action.

### 7.3.7 NVM.BLOCK.ATOMIC\_MULTIWRITE\_MAX\_IOS

Requirement: mandatory if ATOMIC\_MULTIWRITE\_CAPABLE (see 7.3.6) is true

ATOMIC\_MULTIWRITE\_MAX\_IOS is the maximum length of the number of IOs (i.e., the size of the Property Group List) that can be transferred by an ATOMIC\_MULTIWRITE action.

## 7.3.8 NVM.BLOCK.ATOMIC\_MULTIWRITE\_MAX\_DATA\_LENGTH

Requirement: mandatory if ATOMIC\_MULTIWRITE\_CAPABLE (see 7.3.6) is true

ATOMIC\_MULTIWRITE\_MAX\_DATA\_LENGTH is the maximum length of data that can be transferred by an ATOMIC\_MULTIWRITE action.

### 7.3.9 NVM.BLOCK.ATOMIC\_MULTIWRITE\_STARTING\_ADDRESS\_GRANULARITY

Requirement: mandatory if ATOMIC\_MULTIWRITE\_CAPABLE (see 7.3.6) is true

ATOMIC\_MULTIWRITE\_STARTING\_ADDRESS\_GRANULARITY is the granularity of the starting address of ATOMIC\_MULTIWRITE inputs. Address inputs to ATOMIC\_MULTIWRITE shall be evenly divisible by ATOMIC\_MULTIWRITE\_STARTING\_ADDRESS\_GRANULARITY.

## 7.3.10 NVM.BLOCK.ATOMIC\_MULTIWRITE\_LENGTH\_GRANULARITY

Requirement: mandatory if ATOMIC\_MULTIWRITE\_CAPABLE (see 7.3.6) is true

ATOMIC\_MULTIWRITE\_LENGTH\_GRANULARITY is the granularity of the length of ATOMIC\_MULTIWRITE inputs. Length inputs to ATOMIC\_MULTIWRITE shall be evenly divisible by ATOMIC\_MULTIWRITE\_LENGTH\_GRANULARITY.

#### 7.3.11 NVM.BLOCK.WRITE\_ATOMICITY\_UNIT

Requirement: mandatory

If a write is submitted of this size or less, the caller is guaranteed that if power is lost before the data is completely written, then the NVM device shall ensure that all the logical blocks affected by the operation contain the data that was present before the device server started processing the write operation (i.e., the old data, as if the atomic write operation had no effect).

If the NVM device can't assure that at least one LOGICAL\_BLOCKSIZE (see 7.3.14) extent can be written atomically, WRITE\_ATOMICITY\_UNIT shall be set to zero.

The unit is NVM.BLOCK.LOGICAL\_BLOCKSIZE (see 7.3.14).

#### 7.3.12 NVM.BLOCK.EXISTS\_CAPABLE

Requirement: mandatory

This attribute indicates that the implementation is capable of the NVM.BLOCK.EXISTS action.

#### 7.3.13 NVM.BLOCK.SCAR\_CAPABLE

Requirement: mandatory

This attribute indicates that the implementation is capable of the NVM.BLOCK.SCAR (see 7.2.7) action.

#### 7.3.14 NVM.BLOCK.LOGICAL\_BLOCK\_SIZE

Requirement: mandatory

LOGICAL\_BLOCK\_SIZE is the smallest unit of data (in bytes) that may be logically read or written from the NVM volume.

#### 7.3.15 NVM.BLOCK.PERFORMANCE\_BLOCK\_SIZE

Requirement: mandatory

PERFORMANCE\_BLOCK\_SIZE is the recommended granule (in bytes) the caller should use in I/O requests for optimal performance; starting addresses and lengths should be multiples of this attribute. For example, this attribute may help minimizing device-implemented read/modify/write behavior.

#### 7.3.16 NVM.BLOCK.ALLOCATION\_BLOCK\_SIZE

Requirement: mandatory

ALLOCATION\_BLOCK\_SIZE is the recommended granule (in bytes) for allocation and alignment of data. Allocations smaller than this attribute (even if they are multiples of LOGICAL\_BLOCK\_SIZE) may work, but may not yield optimal lifespan.

#### 7.3.17 NVM.BLOCK.DISCARD\_IF\_YOU\_CAN\_CAPABLE

Requirement: mandatory

DISCARD\_IF\_YOU\_CAN\_CAPABLE shall be set to true if the implementation supports DISCARD\_IF\_YOU\_CAN.

#### 7.3.18 NVM.BLOCK.DISCARD\_IMMEDIATELY\_CAPABLE

Requirement: mandatory

Returns true if the implementation supports DISCARD\_IMMEDIATELY.

#### 7.3.19 NVM.BLOCK.DISCARD\_IMMEDIATELY\_RETURNS

Requirement: mandatory if DISCARD\_IMMEDIATELY\_CAPABLE (see 7.3.18) is true

The value returned from read operations to blocks specified by a DISCARD\_IMMEDIATELY action with no subsequent write operations. The possible values are:

- A value that is returned to each read of an unmapped block (see NVM.BLOCK.EXISTS 7.2.6) until the next write action

- Unspecified

#### 7.3.20 NVM.BLOCK.FUNDAMENTAL\_BLOCK\_SIZE

Requirement: mandatory

FUNDAMENTAL\_BLOCK\_SIZE is the number of bytes that may become unavailable due to an error on an NVM device.

A zero value means that the device is unable to provide a guarantee on the number of adjacent bytes impacted by an error.

This attribute is relevant when the device does not support write atomicity.

If FUNDAMENTAL\_BLOCK\_SIZE is smaller than LOGICAL\_BLOCK\_SIZE (see 7.3.14), an application may organize data in terms of FUNDAMENTAL\_BLOCK\_SIZE to avoid certain torn write behavior. If FUNDAMENTAL\_BLOCK\_SIZE is larger than LOGICAL\_BLOCK\_SIZE, an application may organize data in terms of FUNDAMENTAL\_BLOCK\_SIZE to assure two key data items do not occupy an extent that is vulnerable to errors.

### 7.4 Use cases

#### 7.4.1 Flash as cache use case

#### Purpose/triggers:

Use Flash based NVM as a data cache.

#### Scope/context:

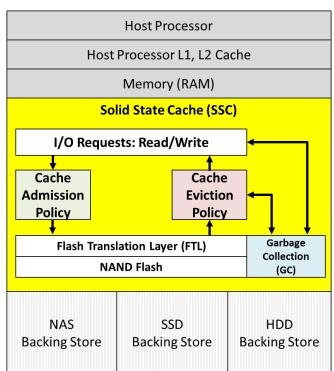

Flash memory's fast random I/O performance and non-volatile characteristic make it a good candidate as a Solid State Cache device (SSC). This use case is described in Figure 7 SSC in a storage stack.

| Host Processor              |                      |                      |  |  |

|-----------------------------|----------------------|----------------------|--|--|

| Host Processor L1, L2 Cache |                      |                      |  |  |

| Memory (RAM)                |                      |                      |  |  |

| Solid State Cache (SSC)     |                      |                      |  |  |

| NAS<br>Backing Store        | SSD<br>Backing Store | HDD<br>Backing Store |  |  |

Figure 7 SSC in a storage stack

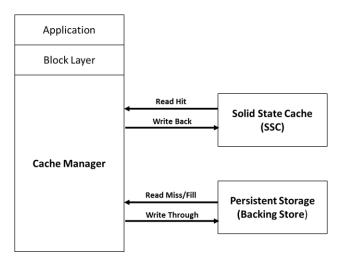

A possible software application is shown in Figure 8 SSC software cache application. In this case, the cache manager employs the Solid State Cache to improve caching performance and to maintain persistence and cache coherency across power fail.

#### Figure 8 SSC software cache application

It is also possible to use an enhanced SSC to perform some of the functions that the cache manager must normally contend with as shown in Figure 9 SSC with caching assistance.

In this use case, the Solid State Cache (SSC) provides a sparse address space that may be much larger than the amount of physical NVM memory and manages the cache through its own admission and eviction policies. The backing store is used to persist the data when the cache becomes full. As a result, the block state for each block of virtual storage in the cache must be maintained by the SSC. The SSC must also present a consistent cache interface that can persist the cached data across a power fail and never returns stale data.

#### Figure 9 SSC with caching assistance

In either of these cases, two important extensions to existing storage commands must be present:

**Eviction:** An explicit eviction mechanism is required to invalidate cached data in the SSC to allow the cache manager to precisely control the contents of the SSC. This means that the SSC must insure that the eviction is durable before completing the request. This mechanism is generally referred to as a persistent trim. This is the NVM.BLOCK.DISCARD\_IMMEDIATELY functionality.

**Exists:** The EXISTS action allows the cache manager to determine the state of a block, or of a range of blocks, in the SSC. This action is used to test for the presence of data in the cache, or to determine which blocks in the SSC are dirty and need to be flushed to backing storage. This is the NVM.BLOCK.EXISTS functionality.

The most efficient mechanism for a cache manager would be to simply read the requested data from the SSC which would the return either the data or an error indicated that the requested data was not in the cache. This approach is problematic, since most storage drivers and software require reads to be successful and complete by returning data - not an error. Device that return errors for normal read operations are usually put into an offline state by the system drivers. Further, the data that a read returns must be consistent from one read operation to the next, provided that no intervening writes occur. As a result, a two stage process must be used by the cache manager. The cache manager first issues an EXISTS action to determine if the requested data is present in the cache. Based on the result, the cache manager decides whether to read the data from the SSC or from the backing storage.

## Success scenario:

The requested data is successfully read from or written to the SSC.

## See also:

- 7.2.5 NVM.BLOCK.DISCARD\_IMMEDIATELY

- 7.2.6 NVM.BLOCK.EXISTS

- Ptrim() + Exists(): Exposing New FTL Primitives to Applications, David Nellans, Michael Zappe, Jens Axboe, David Flynn, 2011 Non-Volatile Memory Workshop. See: <u>http://david.nellans.org/files/NVMW-2011.pdf</u>

- FlashTier: a Lightweight, Consistent, and Durable Storage Cache, Mohit Saxena, Michael M. Swift and Yiying Zhang, University of Wisconsin-Madison. See: <u>http://pages.cs.wisc.edu/~swift/papers/eurosys12\_flashtier.pdf</u>

HEC: Improving Endurance of High Performance Flash-based Cache Devices, Jingpei Yang, Ned Plasson, Greg Gillis, Nisha Talagala, Swaminathan Sundararaman, Robert Wood, Fusion-io, Inc., SYSTOR '13, June 30 - July 02 2013, Haifa, Israel

- Unioning of the Buffer Cache and Journaling Layers with Non-volatile Memory, Eunji Lee, Hyokyung Bahn, and Sam H. Noh. See: https://www.usenix.org/system/files/conference/fast13/fast13-final114\_0.pdf

# 7.4.2 SCAR use case

## Purpose/triggers:

Demonstrate the use of the SCAR action

## Scope/context:

This generic use case for SCAR involves two processes.

- The "detect block errors process" detects errors in certain NVM blocks, and uses SCAR to communicate to other processes that the contents of these blocks cannot be reliably read, but can be safely re-written.

- The "recover process" sees the error reported as the result of SCAR. If this process can regenerate the contents of the block, the application can continue with no error.

For this use case, the "detect block errors process" is a RAID component doing a background scan of NVM blocks. In this case, the NVM is not in a redundant RAID configuration so block READ errors can't be transparently recovered. The "recover process" is a cache component using the NVM as a cache for RAID volumes. Upon receipt of the SCAR error on a read, this component evaluates whether the block contents also reside on the cached volume; if so, it can copy the corresponding volume block to the NVM. This write to NVM will clear the SCAR error condition.

## Preconditions:

The "detect block errors process" detected errors in certain NVM blocks, and used SCAR to mark these blocks.

#### Success scenario:

- 1. The cache manager intercepts a read request from an application

- 2. The read request to the NVM cache returns a status indicating the requested blocks have been marked by a SCAR action

- 3. The cache manager uses an implementation-specific technique and determines the blocks marked by a SCAR are also available on the cached volume

- 4. The cache manager copies the blocks from the cached volume to the NVM

- 5. The cache manager returns the requested block to the application with a status indicating the read succeeded

## **Postconditions:**

The blocks previously marked with a SCAR action have been repaired.

## Failure Scenario:

- 1. In Success Scenario step 3 or 4, the cache manager discovers the corresponding blocks on the volume are invalid or cannot be read.

- 2. The cache manager returns a status to the application indicating the blocks cannot be read.

# 8 NVM.FILE mode

# 8.1 Overview

NVM.FILE mode addresses NVM-specification extensions to native file I/O behavior (the approach to I/O used by most applications). Support for NVM.FILE mode requires that the NVM solution ought to support all behavior not covered in this section consistently with the native operating system behavior for native block devices.

# 8.1.1 Discovery and use of atomic write features

Atomic Write features in NVM.FILE mode are available to block-optimized applications (see 7.1.4.2 Block-optimized applications).

# 8.1.2 The discovery of granularities

The NVM.FILE mode exposes the same granularity attributes as NVM.BLOCK.

# 8.1.3 Relationship between native file APIs and NVM.BLOCK.DISCARD

NVM.FILE mode does not define specific action that cause TRIM/DISCARD behavior. File systems may invoke NVM.BLOCK DISCARD actions when native operating system APIs (such as POSIX truncate or Windows SetEndOfFile).

# 8.2 Actions

## 8.2.1 Actions that apply across multiple modes

The following actions apply to NVM.FILE mode as well as other modes.

NVM.COMMON.GET\_ATTRIBUTE (see 6.11.1) NVM.COMMON.SET\_ATTRIBUTE (see 6.11.2)

# 8.2.2 NVM.FILE.ATOMIC\_WRITE

Requirement: mandatory if ATOMIC\_WRITE\_CAPABLE (see 8.3.2) is true

Block-optimized applications may use ATOMIC\_WRITE to assure consistent behavior during a failure condition. This specification does not specify the order in which this action occurs relative to other I/O operations, including other ATOMIC\_WRITE and ATOMIC\_MULTIWRITE actions. This specification does not specify when the data written becomes visible to other threads.

The inputs, outputs, and error conditions are similar to those for NVM.BLOCK.ATOMIC\_WRITE, but typically the application provides file names and file relative block addresses rather than device name and LBA.

Relevant attributes:

ATOMIC\_WRITE\_MAX\_DATA\_LENGTH ATOMIC\_WRITE\_STARTING\_ADDRESS\_GRANULARITY ATOMIC\_WRITE\_LENGTH\_GRANULARITY ATOMIC\_WRITE\_CAPABLE

# 8.2.3 NVM.FILE.ATOMIC\_MULTIWRITE

Requirement: mandatory if ATOMIC\_MULTIWRITE\_CAPABLE (see 8.3.6) is true

Block-optimized applications may use ATOMIC\_MULTIWRITE to assure consistent behavior during a failure condition. This action allows a caller to write non-adjacent extents atomically. The caller of ATOMIC\_MULTIWRITE provides properties defining memory and block extents; all of the extents are written as a single atomic operation. This specification does not specify the order in which this action occurs relative to other I/O operations, including other ATOMIC\_WRITE and ATOMIC\_MULTIWRITE actions. This specification does not specify when the data written becomes visible to other threads.

The inputs, outputs, and error conditions are similar to those for NVM.BLOCK.ATOMIC\_MULTIWRITE, but typically the application provides file names and file relative block addresses rather than device name and LBA.

Relevant attributes:

ATOMIC\_MULTIWRITE\_MAX\_IOS ATOMIC\_MULTIWRITE\_MAX\_DATA\_LENGTH ATOMIC\_MULTIWRITE\_STARTING\_ADDRESS\_GRANULARITY ATOMIC\_MULTIWRITE\_LENGTH\_GRANULARITY ATOMIC\_MULTIWRITE\_CAPABLE

# 8.3 Attributes

Some attributes share behavior with their NVM.BLOCK counterparts. NVM.FILE attributes are provided because the actual values may change due to the implementation of the file system.

## 8.3.1 Attributes that apply across multiple modes

The following attributes apply to NVM.FILE mode as well as other modes.

NVM.COMMON.SUPPORTED\_MODES (see 6.12.1) NVM.COMMON.FILE\_MODE (see 6.12.2)

#### 8.3.2 NVM.FILE.ATOMIC\_WRITE\_CAPABLE

Requirement: mandatory

This attribute indicates that the implementation is capable of the NVM.BLOCK.ATOMIC\_WRITE action.

## 8.3.3 NVM.FILE.ATOMIC\_WRITE\_MAX\_DATA\_LENGTH

Requirement: mandatory

ATOMIC\_WRITE\_MAX\_DATA\_LENGTH is the maximum length of data that can be transferred by an ATOMIC\_WRITE action.

## 8.3.4 NVM.FILE.ATOMIC\_WRITE\_STARTING\_ADDRESS\_GRANULARITY

Requirement: mandatory

ATOMIC\_WRITE\_STARTING\_ADDRESS\_GRANULARITY is the granularity of the starting memory address for an ATOMIC\_WRITE action. Address inputs to ATOMIC\_WRITE shall be evenly divisible by ATOMIC\_WRITE\_STARTING\_ADDRESS\_GRANULARITY.

## 8.3.5 NVM.FILE.ATOMIC\_WRITE\_LENGTH\_GRANULARITY

Requirement: mandatory

ATOMIC\_WRITE\_LENGTH\_GRANULARITY is the granularity of the length of data transferred by an ATOMIC\_WRITE action. Length inputs to ATOMIC\_WRITE shall be evenly divisible by ATOMIC\_WRITE\_STARTING\_ADDRESS\_GRANULARITY.

#### 8.3.6 NVM.FILE.ATOMIC\_MULTIWRITE\_CAPABLE

Requirement: mandatory

This attribute indicates that the implementation is capable of the NVM.FILE.ATOMIC\_MULTIWRITE action.

## 8.3.7 NVM.FILE.ATOMIC\_MULTIWRITE\_MAX\_IOS

Requirement: mandatory

ATOMIC\_MULTIWRITE\_MAX\_IOS is the maximum length of the number of IOs (i.e., the size of the Property Group List) that can be transferred by an ATOMIC\_MULTIWRITE action.

# 8.3.8 NVM.FILE.ATOMIC\_MULTIWRITE\_MAX\_DATA\_LENGTH

Requirement: mandatory

ATOMIC\_MULTIWRITE\_MAX\_DATA\_LENGTH is the maximum length of data that can be transferred by an ATOMIC\_MULTIWRITE action.

# 8.3.9 NVM.FILE.ATOMIC\_MULTIWRITE\_STARTING\_ADDRESS\_GRANULARITY

Requirement: mandatory

ATOMIC\_MULTIWRITE\_STARTING\_ADDRESS\_GRANULARITY is the granularity of the starting address of ATOMIC\_MULTIWRITE inputs. Address inputs to ATOMIC\_MULTIWRITE shall be evenly divisible by ATOMIC\_MULTIWRITE\_STARTING\_ADDRESS\_GRANULARITY.

## 8.3.10 NVM.FILE.ATOMIC\_MULTIWRITE\_LENGTH\_GRANULARITY

Requirement: mandatory