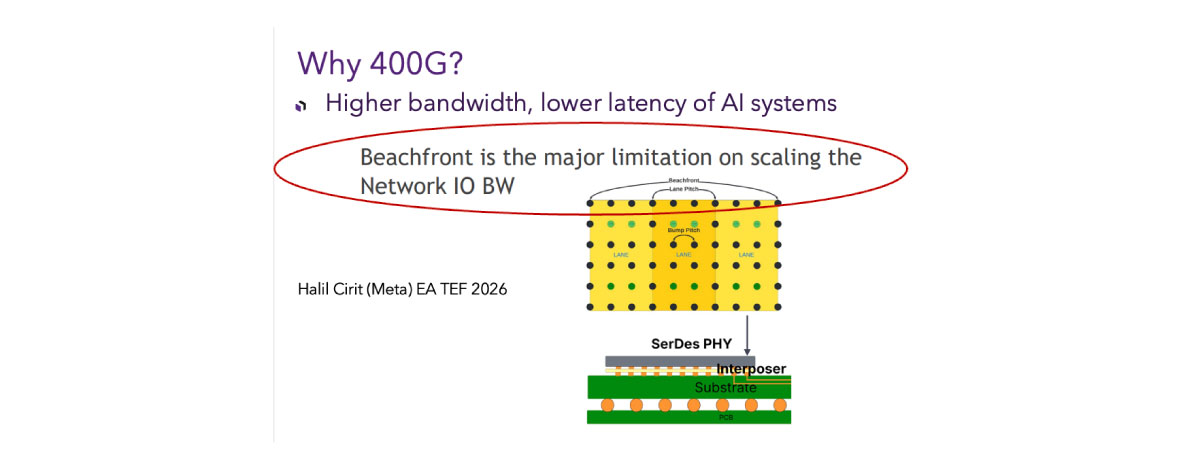

The SNIA Data, Networking & Storage Community recently hosted a live webinar, “Accelerating AI Infrastructure: The Role of 400G and PCIe 8.0 in Next-Gen Interconnects” with experts, Anthony Constantine and Tom Palkert. Anthony and Tom delivered an introduction into physical infrastructure, copper connections and the challenges to 400G, PCIe cabling to SSDs and the road to PCIe 8.0, the inflection point of copper and optical, and AI needs of SSDs. If you missed the session, you can access It in the SNIA Educational Library along with slides. It was a fascinating session with a lot of questions from the audience that Anthony and Tom have answered here.

Q: The Nyquist frequency of PCIe 8 is expected to be 64 GHz. Does that assume PCIe 8 continues to use PAM4? If PAM6 is used, would that would reduce the Nyquist frequency to 48 GHz, is that correct?

A: Nyquist frequency for PCIe is expected to be 64 GHz. Does it assume PCIe 8 continues to use PAM 4? The expectation right now for PCIe 8 is that it would continue to use PAM 4.

Q: Will the SSD cold plate standards sink the thermal load into the chassis? That is, will the chassis be responsible for providing the dissipation of the SSD heat sunk into the cold plate?

A: That is correct. The host chassis will conduct the heat away from the SSD by using a cold plate or some cooling structure, making direct contact with the SSD enclosure.

Q: Do all thicknesses of E1.S support cold plate cooling?

A: Thicknesses of E1.S do not support cold plate cooling. What we've been focused on as an industry is one SKU or one version of the device per spec. So, for instance, E3.S and E3.L are focused on one thickness. E1.S is focused on one thickness. For E1.S, it's the 9.5 millimeter. For E3.S and E3.L, it's the 7.5 millimeter.

Q: What are the mechanical & cost increases for replacing back plane with connector? Some back planes used to have additional circuit to cleanup supply power, how will that be implemented in 2 connector topologies?

A: As far as the mechanical and cost increases for replacing a back plane with connector, I would actually argue that you're going from a back plane to a midplane (a PCB parallel to the host motherboard. Because you still have this midplane, you would have a lot of that same circuitry on that midplane. The midplane though would not need to support the high speed signaling, so cheaper PCB materials and less layers are possible. So, that midplane would actually have a lower cost overall. You're reducing the cost of going from a back plane to a midplane

Q: Is there any use-case where the noisy PAM8 would be practically useful with no specialized error/noise correction mechanism to assist? Just want to compare viability with PAM4 which has near-zero SNR.

A: It would be difficult to see how PAM8 could be used without error correction at any high-speed data rate (above 10 Gbps). It is especially difficult for optical systems which tend to be noise limited.

Q: Considering that PAM8 reduces the SNR (Signal-to-Noise Ratio) by 6.3 dB compared to PAM4, how robust is this modulation against physical channel imperfections in real-world deployments, or is it limited only to very short distances?

A: PAM8 should be considered if the insertion loss of the channel measured between the Nyquist frequencies for PAM4/6/8 exceeds the 6.3dB SNR reduction. There are other factors involved but insertion loss is the primary driver. For 400G we see channels that would seem to benefit from PAM8 but the SNR hit is tough. This is why the compromise to PAM6 is being strongly considered.

Q: [In jest] you are making the case for HBF here on slide 34.

A: HBF - I'm not going to comment on that as we showed earlier that there are enablers to get SSDs to run at PCIe8 and beyond.

This webinar is part of our “AI Stack Webinar Series.” You can check out the webinars to date at the SNIAVideo YouTube Channel. We encourage you to follow us on LinkedIn and @SNIA for upcoming dates and topics.

Leave a Reply